# DESIGN AND VERIFICATION OF LOW POWER AND HIGH SPEED CARRY SELECT ADDER USING VERILOG

Bejagam Divya<sup>1</sup>, Alekhya Bonkuri<sup>2</sup>, Madhavi Bandi<sup>3</sup>, Somashekar Malipatil<sup>4</sup>

<sup>1,2,3</sup>B.Tech Scholars, <sup>4</sup>Assistant Professor Department of Electronics and Communication Engineering Nalla Malla Reddy Engineering College, Hyderabad, India

Abstract—There is a vast usage of binary addition in digital circuits as it is the basic arithmetic operation and it became indispensable in most of the digital systems counting ALU, microprocessors and DSP. Adders are the fundamental building blocks in digital integrated circuit based designs. Ripple Carry Adder (RCA) gives the most solid design but takes more computation time. The time crucial applications employ Carry Look-ahead scheme (CLA) is used to derive fast results but they lead to increase in area. Carry Select Adder is a concession between RCA and CLA in terms of area and delay. This paper shows a great vision on the design analysis of carry select adder based on Multiplexer using Verilog. The delay (9.069ns), power (20.98mW) is minimized and total coverage is 100%. The proposed architecture of carry select adder is simulated and verified in ModelSim10.1e, synthesized in Xilinx ISE14.7 and power analyzed in Quartus II9.1.

*Keywords*—Carry select adder, Verilog, Power, delay, Modelsim10.1e, Xilinx ISE14.7, QuartusII9.1, Fulladder, Carry ripple adder, multiplexer.

#### I. Introduction

Devices like digital computers, processors, microprocessors often use arithmetic operations. Among those arithmetic operations addition is most commonly used. Also it serves as a edifice block for synthesis all other arithmetic operations. In digital adders, the speed of the adders is limited to propagate a carry through the adder. In elementary adder the sum of each bit position is generated sequentially only after the previous bit position has been summed and carry is propagated to next The major speed limitation in any adder is in the adder. production of carries. The carry select adder is used in many computational systems to overcome the problem of carry propagation delay. Power consumption is a major factor in very large scale integrated (VLSI) circuit.. The central electronic circuit used for addition is adder. Adders are fundamental for wide variety of digital system. In existing adders the fast adding and consumption of low power is still challenging.

## II. Proposed work

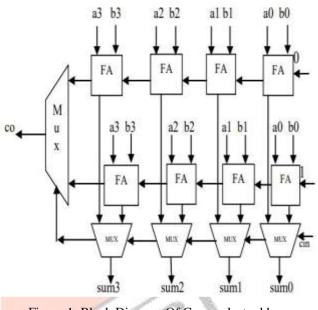

Figure 1: Block Diagram Of Carry select adder.

The design of 4-bit carry-select adder consists of two ripple carry adders and five multiplexers in that four are used for sum calculation and one for carry output. Adding two n-bit numbers with a carry-select adder is done with two adders in order to perform the calculation twice, one time with the assumption of the carry being zero and the other assuming one. After the two results are calculated, by using multiplexers the correct sum and carry is selected once the correct carry is known. The number of bits in each carry select block can be uniform, or variable. When variable, the chunk size should have a delay, from addition inputs "a" and "b" to the carry out, equal to that of the multiplexer chain leading into it, so that the carry out is calculated just in time. The delay is derived from standardized sizing, where the superlative number of fulladder elements per block is equal to the square root of the number of bits being added, since that will defer an equal number of Mux delays. However, the carry select adder is not area efficient because it uses multiple pairs of Ripple Carry Adders to generate partial sum and carry by considering carry input and then the final sum and carry are selected by the multiplexers.

This design has efficiently decreased the delay there by increasing the speed making it a high speed carry select adder. The factor which are advantageous in adders are as follows:

➢ High speed

Low power consumption

### III. Synthesis Results

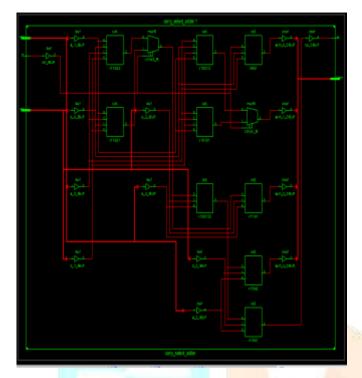

Figure 2: Technology view map of carry select adder.

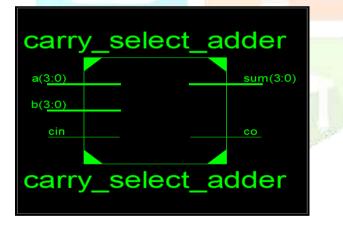

Figure 3:Top module of carry select adder.

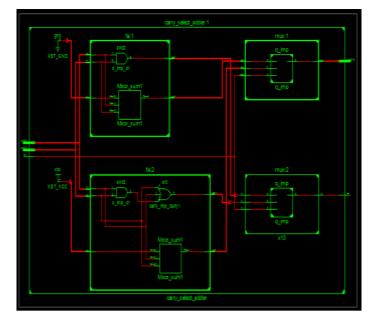

Figure 4: RTL schematic of carry select adder.

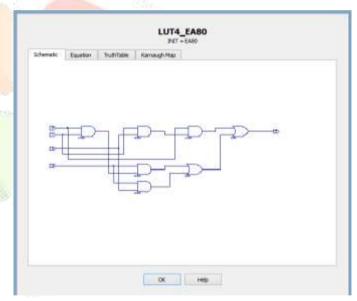

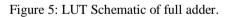

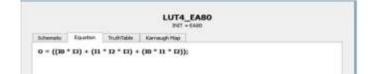

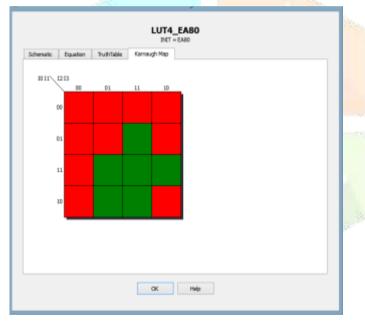

#### Considering one Look up table of full adder:

Figure 6: LUT Equation of full adder.

1787

| ethore into 1 | - Processor                     | TruthTable   | -                                    |                                                                              |   |

|---------------|---------------------------------|--------------|--------------------------------------|------------------------------------------------------------------------------|---|

| Schenatic     | Equation                        | manape       | Kamaugh Map                          |                                                                              |   |

| 15            | 12                              | 18           | 10                                   | 0                                                                            |   |

| Û.            | 0                               | 0            | 0                                    | 0                                                                            |   |

| 0             | 0                               | 0            | 0                                    | 0                                                                            |   |

| 0             | 0                               | 1            |                                      | 0                                                                            |   |

| 0             | 0<br>0<br>1                     | 1            | 1                                    | 0                                                                            |   |

| 0             | 1                               | Ø.           | 0                                    | 0                                                                            |   |

| 0             | 1                               | 0            |                                      | 0                                                                            |   |

| σ             | 1                               | 1            | 0                                    | 0                                                                            |   |

| 0             | 1                               | 10           |                                      | 1                                                                            |   |

| 1             | T<br>0<br>0<br>0<br>T<br>1<br>T | 001100110011 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | D<br>D<br>D<br>D<br>D<br>1<br>1<br>D<br>1<br>1<br>0<br>1<br>1<br>1<br>1<br>1 |   |

| 1             | 0                               | 0            | 1                                    | 1                                                                            |   |

| 1             | 0                               | 1            |                                      | 0                                                                            |   |

| 3             | 0                               | 1            | 1                                    |                                                                              |   |

| 1             | 1                               | 0            |                                      | 0                                                                            |   |

| 1             |                                 | 0            | 1                                    |                                                                              |   |

| 1             | 1                               | - 21         | 2                                    |                                                                              |   |

| 1             |                                 |              | 10                                   |                                                                              |   |

|               |                                 |              |                                      |                                                                              |   |

|               |                                 |              |                                      |                                                                              |   |

|               |                                 |              |                                      |                                                                              |   |

|               |                                 |              |                                      |                                                                              |   |

| ¢ .           |                                 |              |                                      |                                                                              | ÷ |

Figure 7: LUT Truth table of full adder.

#### **IV. Synthesis report**

#### **Delay analysis:**

Timing Summary: Speed Grade: -4 Maximum combinational path delay: 9.069ns Timing Detail: All values displayed in nanoseconds (ns) Timing constraint: Default path analysis Total number of paths / destination ports: 49 / 5

Delay: 9.069ns (Levels of Logic = 6) Source: b < 1 > (PAD)Destination: co (PAD)

| Data Path: b< | 1> to co     |              |             |           |

|---------------|--------------|--------------|-------------|-----------|

| Gate Net      |              |              |             |           |

| Cell:in->out  | fanout       | Delay        | Delay       | Logical   |

| Name          |              |              |             |           |

| IBUF:I->O     | 4 1.218      | 0.762 b_1_l  | BUF         |           |

| LUT4:I0->O    | 1 0.704      | 0.000        | x11/q31     |           |

| MUXF5:I1->0   | O 2 0.321    | 0.482 x11/c  | 13_f5 (N10) |           |

| LUT3:I2->O    | 2 0.704      | 0.482 x12/q1 | 33 (N2) LU  | JT3:I2->O |

| 1 0.704 0.42  | 20 x13/q1 (o | co_OBUF)     |             |           |

| OBUF:I->O     | 3.27         | 72 co_Ol     | BUF (co)    |           |

|               |              |              |             |           |

|               | 0.0.10       |              |             |           |

Total 9.069ns (6.923ns logic, 2.146ns route) (76.3% logic, 23.7% route)

#### Device utilization summary:

Selected Device : 3s500efg320-4

Number of Slices:5 out of46560%Number of 4 input LUTs:9 out of93120%Number ofIOs:141414 out of2326%

Total memory usage is 232188 kilobytes

#### Final report:

RTL Top Level Output File Name : carry\_select\_ adder.ngr Top Level Output File Name : carry\_select\_adder **Output Format** : NGC **Optimization** Goal : Speed Keep Hierarchy : No **Design Statistics** # IOs **Cell Usage : # BELS** # LUT3 : 5 # LUT4 :4 # MUXF5 :2 # IO Buffers :14

:9

: 5

#### **Power analysis:**

**IBUF**

OBUF

#

#

| PowerPlay Power Analyzer Status        | Successful - Mon Feb 26 14:23:10 2018            |

|----------------------------------------|--------------------------------------------------|

| Quartus II Version                     | 9.1 Build 222 10/21/2009 SJ Web Edition          |

| Revision Name                          | carry_select_adder                               |

| Top-level Entity Name                  | carry_select_adder                               |

| Family                                 | Stratix II                                       |

| Device                                 | EP2S15F484C3                                     |

| Power Models                           | Final                                            |

| Total Thermal Power Dissipation        | 323.95 mW                                        |

| Core Dynamic Thermal Power Dissipation | 0.00 mW                                          |

| Core Static Thermal Power Dissipation  | 302.97 mW                                        |

| I/O Thermal Power Dissipation          | 20.98 mW                                         |

| Power Estimation Confidence            | Low: user provided insufficient toggle rate data |

Figure 9: power analysis in QuartusII9.1.

The I/O Thermal power dissipation is 20.98 mW when compared to previously proposed papers.

#### V. Simulation results

| <b>×</b>                                                              | Msgs              |              |

|-----------------------------------------------------------------------|-------------------|--------------|

| <ul> <li>/cstest/a</li> <li>/cstest/b</li> <li>/cstest/cin</li> </ul> | 1110<br>1011<br>0 | 1110<br>1011 |

| /cstest/sum<br>/cstest/co                                             | 1001<br>St1       | 1001         |

|                                                                       |                   |              |

|                                                                       |                   |              |

Figure 10: Simulation results of carry select adder.

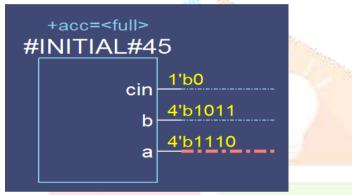

The results are obtained by simulating the verilog code in ModelSim 10.1e. In the above figure , the inputs are a=1110, b=1011 and cin=0 and the output sum=1001 and carry=1

Figure 11: Data flow model of carry select adder at input side.

Figure 12: Data flow model of carry select adder.

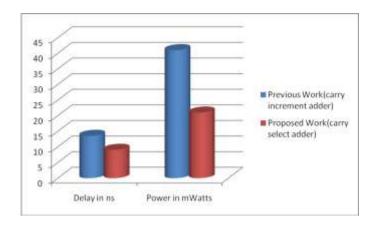

#### Comparison

| Parameter       | Previous<br>work(2016) | Proposed<br>work(2018) |

|-----------------|------------------------|------------------------|

| Delay in ns     | 13.54                  | 9.06                   |

| Power in mWatts | 41                     | 20.98                  |

#### **VI. Verification Result**

| report.txt               |            |           |             |         | 2 |

|--------------------------|------------|-----------|-------------|---------|---|

| overage Report Totals BY | INSTANCES: | Number of | Instances   | 15      |   |

| Enabled Coverage         | Active     | Hits      | Hinnes b    | Covered |   |

|                          |            |           |             |         |   |

| Stata                    | 0          | 0         | 0           | 100.0   |   |

| Branches                 | 0          | 0         | 0           | 100.0   |   |

| UDP Condition Rows       |            |           | 0           | 100.0   |   |

| FEC Condition Terms      | 0          | 0         | 0           | 100.0   |   |

| UDP Expression Rows      | 0          | 0         |             | 100.0   |   |

| FEC Expression Terms     | 0000       | a<br>a    | 0<br>0<br>0 | 100.0   |   |

| States                   | 0          | 0         | D           | 100.0   |   |

| Trensitions              | 0          | 0         | 0           | 100.0   |   |

| Toggle Bins              | 0          | 0         | 0           | 100.0   |   |

|                          |            |           |             |         |   |

|                          |            |           |             |         |   |

|                          |            |           |             |         |   |

Figure14: verification results in ModelSim10.1e.

The above figure shows the verification report of total coverage area of instances.

#### VII. Conclusion

The proposed design of carry select adder is simulated in ModelSim10.1, synthesized in Xilinx ISE 14.7 and power analysis is done using Quartus II9.1. The source code is written in Verilog. As we know Delay, Power and area are the major factors in VLSI design that limits the performance of any circuit. This paper concentrates more on power and speed by presenting a simple approach to reduce the delay and power of Carry select adder architecture, which helps in increasing the computational level of calculations. This proposed carry select adder has delay 9.06ns, power 20.98mw and total coverage achieved is 100%.

#### References

[1] Aribam Balarampyari Devi et.al., "Design and implementation of an improved carry increment adder".International journal of VLSI design and communication-systems(VLSICS) Vol.7,No.1,February 2016.

CR

- [2] Satinder Singh Mohar and Manjith Singh Bhamrah"Area and Delay efficient carry select adder using carry prediction approach".International journal of trends in engineering and technology(IJLTET) ISSN:2278-621X,vol.7, issue 2 july 2016

- [3] Somashekhar Matipatil et.al., "Low Power and High Speed Carry Select Adder Design using Verilog". IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 6, Issue 6, Ver. II (Nov. - Dec. 2016), PP 77-81 e-ISSN: 2319 – 4200

- [4] B. Ramkumarnd Harish M Kittur, "low power and area efficient carry select adder" IEEE transactions on very large scale integration (VLSI) systems, vol. 20, no. 2, February 2012.

- [5] B. Ram Kumar, Kittur, H.M. and Kannan, p. m. (2010) "ASIC implementation of modified faster carry save adder", EUR. j. sci. RES., vol.42, no.1, pp.53–58.

- [6] C.S.Manikandababu "an efficient CSLA architecture for VLSI hardware implementation" IJMIE, ISSN: 2249-0558, volume 2, issue 5, 2012, pp.610-622.

- [7] Arunprasath S et al., "VLSI implementation and analysis of parallel adders for low power applications", international journal of computer science and mobile computing, vol.3 issue.2, February- 2014, pg. 181-186.

- [8] Shivani Parmar and Kiratpal Singh," design of high speed hybrid carry select adder", IEEE's 3<sup>rd</sup> international advance computing conference Ghaziabad, ISBN: 978-1-4673-4527-9, 22-23 february2013.