# Recent Advancements In SSD Firmware For Enhanced Performance, Endurance And Reliability

Arjun Singh\*, Dr. Hemalatha J N ‡

\*Electrical and Electronic Engineering, R V College of Engineering

‡ Associate Professor

Electrical and Electronic Engineering, R V College of Engineering

Abstract—Solid State Drives (SSDs) have revolutionized data storage by providing faster access speeds, lower power consumption, and greater durability compared to traditional Hard Disk Drives (HDDs). At the heart of SSD performance lies the firmware, which manages complex operations such as Flash Translation Layer (FTL), wear leveling, garbage collection, and error correction to maintain device reliability and longevity. This paper presents an in-depth survey of recent advancements in SSD firmware design, focusing on how firmware algorithms address NAND flash memory challenges like limited write endurance and data retention issues. We explore emerging techniques including adaptive firmware tuning powered by artificial intelligence, Zoned Namespace (ZNS) support for improved storage efficiency, and integration of blockchain technology for secure firmware updates. The paper also reviews state-of-the-art simulation and validation frameworks that accelerate firmware development and testing. Through detailed analysis of these innovations, we demonstrate how firmware improvements enable SSDs to meet the growing demands of applications ranging from enterprise data centers to mobile and IoT devices. This comprehensive overview aims to guide researchers and developers in understanding current trends and future directions in SSD firmware technologies.

Keywords—Solid State Drives (SSD), Flash Translation Layer (FTL), NAND Flash Memory, Firmware Architecture, Write Amplification, Wear Leveling, Garbage Collection, Error Correction Code (ECC), Zoned Namespace (ZNS), Firmware Security, AI-assisted Firmware, Blockchain, SSD Simulation, Power-Loss Protection, NVMe.

### I. INTRODUCTION TO SSD FIRMWARE

Solid State Drives (SSDs) have become a cornerstone of modern storage solutions, deployed widely from personal devices to large data centers. Unlike Hard Disk Drives (HDDs), SSDs store data on NAND flash memory, which has no mechanical parts, enabling higher speeds and greater robustness[4],[10]. However, NAND flash is inherently complex, suffering from issues such as limited Program/Erase (P/E) cycles, wear-out, and bit errors. The SSD firmware plays a critical role in managing these limitations by implementing the Flash Translation Layer (FTL), wear leveling, garbage collection (GC), and error correction [1],[15].

Key firmware components include the Flash Translation Layer (FTL), wear levelling algorithms, garbage collection routines, and error correction modules. The FTL maps logical block addresses from the host to physical flash locations, enabling efficient writes despite flash memory's erase-before- write constraints. Wear levelling balances cell usage to pre- vent premature wear, while garbage collection consolidates valid data and frees blocks for new writes, minimizing write amplification. Error correction codes embedded in firmware safeguard data reliability by correcting bit errors arising from flash degradation.

The continuous demand for higher performance, reliability, and longevity in SSDs has driven innovations in firmware design. From the first-generation page-level mapping FTLs to advanced multi-core controllers with hardware accelerators, firmware architectures have evolved to exploit hardware parallelism, optimize write amplification, and enhance endurance[6],[9],[10]. This paper reviews these recent advancements, emphasizing their practical impact and the simulation tools aiding firmware development.

### II. HISTORICAL EVOLUTION OF SSD FIRMWARE

### A. Early Firmware Models and Limitations

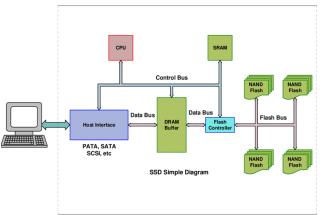

The initial SSDs employed simplistic firmware mainly based on page-level or block-level mapping FTLs, which directly translated logical block addresses (LBAs) to physical NAND locations [15]. While straightforward, this approach had drawbacks: high memory overhead for mapping tables and increased write amplification due to poor data locality awareness. Moreover, garbage collection was rudimentary, often leading to latency spikes during background cleanup operations[9]. Figure 1 illustrates a typical architecture of SSD

firmware, highlighting the limited data flow and functionality.

Fig. 1. Simplified architecture of SSD Firmware

### B. Progression to Dynamic and Hybrid FTL Schemes

To address the growing demand for endurance and performance, SSD firmware evolved to support dynamic FTLs, which allowed remapping of logical pages to different physical locations. Hybrid FTLs later emerged, combining static and dynamic mapping regions to optimize both hot and cold data placement. These developments significantly reduced write amplification and extended SSD lifetime. To address memory overhead and improve efficiency, Demand-based FTL (DFTL) emerged. DFTL caches only frequently accessed mapping entries in RAM, fetching others on demand from NAND, striking a balance between memory usage and performance [9]. This significantly reduced RAM requirements and improved scalability for large SSDs.

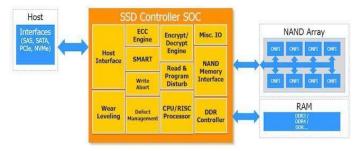

Hybrid FTLs combine page and block mapping, assigning cold data to block mapping and hot data to page mapping, thus optimizing wear and reducing garbage collection frequency [15]. Figure 2 illustrates this hybrid architecture where firmware orchestrates both logical management and real-time hardware acceleration.

Fig. 2. Hybrid Firmware-Hardware Co-Design

C. Hardware- Accelerated and Multi-Core Controllers

Recent SSD controllers integrate multiple CPU cores and dedicated hardware accelerators for ECC, garbage collection, and encryption, enabling parallel execution of firmware tasks[6],[10]. This architecture reduces firmware-induced latency and improves throughput.

### D. Simulation Platforms for Firmware Validation

Due to the complexity of firmware development, simulation environments like FlashSim, FEMU, and QEMU-based SoftSSD are extensively used to model and validate firmware algorithms before hardware deployment[7],[12]. These platforms allow controlled experimentation with different FTL schemes, garbage collection policies, and error correction techniques.

### E. Milestones in Firmware Sophistication

Modern SSD firmware has evolved significantly, transforming from a simple control layer into a sophisticated software stack that actively manages key aspects of storage reliability, endurance, and performance. The following features highlight this progression:

- Background Garbage Collection: Frees up invalid data blocks in the background to ensure efficient use of flash memory.

- Block-level Wear Levelling: Distributes write/erase cycles evenly across memory blocks to extend SSD lifespan.

- Advanced Error Correction: Utilizes powerful schemes like BCH and LDPC codes to detect and correct multi-bit errors.

- Over-Provisioning: Reserves extra storage space to im- prove performance and endurance under heavy work- loads.

- **Thermal Throttling:** Monitors temperature and dynamically reduces performance to prevent overheating.

## III. PERFORMANCE OPTIMIZATION TECHNIQUES

### A. Write Amplification and Garbage Collection

Write Amplification (WA) is a critical factor limiting SSD performance and endurance. It arises when the SSD writes more data to NAND than the host requests, mainly due to out-of-place updates and garbage collection [1],[10].

Advanced garbage collection policies are designed improve endurance. to minimize WA by identifying and cleaning blocks with a high ratio of invalid pages efficiently[12], [17]. Lazy garbage collection defers cleaning to less busy periods, improving user I/O performance.

Check (LDPC) code

Data separation techniques classify hot and cold data based on access frequency and store them in separate physical blocks to reduce invalidations and unnecessary data movement[14].

Due to the limited number of P/E cycles NAND cells can endure, wear leveling is fundamental to extending SSD lifetime [3],[10]. Static wear leveling periodically moves infrequently updated data to ensure even wear distribution, whereas dynamic wear leveling focuses on balancing writes among blocks currently in use.

### B. Over-Provisioning and Auto-Tuning FTLs

Over-provisioning reserves extra NAND capacity beyond the advertised storage to improve garbage collection efficiency and wear leveling [10]. Recent firmware designs include adaptive over-provisioning where the firmware dynamically adjusts reserved space based on workload characteristics to optimize performance and endurance [1].

AutoFTL frameworks utilize machine learning to automatically tune FTL parameters, garbage collection thresholds, and wear-leveling policies tailored to specific workloads, leading to consistent performance improvements[28].

### C. Exploiting Parallelism

Modern SSDs exploit inherent NAND parallelism at multiple levels — across channels, dies, and planes — to maximize throughput [6],[19]. Firmware schedulers distribute I/O requests across these parallel units to prevent bottlenecks and ensure balanced usage.

Multi-queue and out-of-order execution models in

firmware further enhance parallelism, reducing latency and improving quality of service [10].

### D. Write Caching and Reduction Techniques

Temporal locality prediction allows firmware to use write caches to absorb frequent small writes, reducing direct NAND writes and thus wear \[9]. Combined with compression and deduplication at the firmware layer, these techniques significantly improve endurance.

### E. Error Correction and Retention Management

Advanced ECC schemes like Low-Density Parity-Check (LDPC) codes provide robust error correction at high bit error rates, compensating for NAND degradation over time[3],[4]. Firmware integrates these ECC engines with adaptive read voltage adjustment and refresh policies to maintain data integrity [3].

Retention-aware refresh mechanisms periodically rewrite data before retention errors accumulate, further prolonging data reliability[10].

## IV. CURRENT CHALLENGES IN SSD FIRMWARE DEVELOPMENT

# A. Scalability with Increasing NAND Densities (QLC, PLC)

As NAND technology advances from MLC to QLC and PLC, each cell stores more bits, significantly reducing endurance and increasing error rates. Firmware must manage higher raw bit error rates (RBER) while ensuring data integrity through stronger ECC and tighter read/write management. This complexity challenges firmware scalability and impacts latency, especially in low-endurance applications.

# B. Managing Firmware Complexity and Real-Time Constraints

Modern SSD firmware incorporates intricate modules for FTL, wear leveling, GC, and ECC, often executing con- currently. Meeting strict timing constraints while balancing performance and reliability becomes difficult as complexity increases. Real-time performance guarantees are particularly critical in enterprise and real-time systems, requiring lightweight yet intelligent firmware scheduling.

# C. Handling Nondeterministic I/O Workloads and Latency Spikes

Workload unpredictability, especially in data centers, can cause SSDs face unpredictable access patterns due to workload diversity across client and datacenter environments. Internally triggered operations (like GC or wear levelling) may interrupt user I/O, leading to latency spikes. Achieving consistent Quality of Service (QoS) while handling these background tasks remains an open challenge in firmware design.

# D. Firmware Update Risks and Reliability Concerns

Firmware updates are essential for bug fixes and performance improvements but pose risks like bricking or data corruption if interrupted. Reliable update mechanisms with rollback support, cryptographic validation, and redundant firmware images are necessary to ensure secure and fail-safe updates, especially in distributed environments.

### E. Security Vulnerabilities and Firmware Attack Surfaces

SSD firmware has emerged as a critical attack vector due to its low-level control and often proprietary nature. Threats include firmware-level backdoors, unauthorized modifications, and buffer overflow exploits. Secure boot mechanisms, signed firmware images, and runtime integrity checks are essential but not yet universally adopted across all vendors.

### V. RELIABILITY AND SECURITY

### A. Power-Failure Protection

Unexpected power loss can corrupt data and firmware metadata. Modern SSD firmware includes mechanisms like journaling, checkpointing, and power-loss protection capacitors or batteries to safely complete or rollback in-flight operations [6], [22].

Firmware algorithms prioritize atomicity and consistency in metadata updates, using techniques such as transactional writes and metadata redundancy[6].

### B. Bad Block Management and Health Monitoring

Firmware continuously monitors NAND blocks, marking those exhibiting excessive errors as bad and reallocating data to healthy blocks[3]. Health monitoring tools report SMART (Self-Monitoring, Analysis, and Reporting Technology) data to the host for predictive failure analysis.

### C. Firmware Verification and Testing

Robust firmware verification methods such as formal verification and fuzz testing are increasingly employed to identify bugs and security vulnerabilities before deployment[6]. Power fault injection testing simulates power loss scenarios to verify recovery mechanisms.

### D. Firmware-Level Encryption and Access Control

Firmware implements hardware-accelerated AES encryption and secure key management to protect stored data \[27]. Secure erase commands and cryptographic erase features enable quick data sanitization without physical overwriting. Access control mechanisms enforce authentication for firmware access and command execution, preventing unauthorized firmware modifications [27].

### E. Secure Firmware Updates with Blockchain

Firmware-over-the-air (FOTA) updates are critical for fixing bugs and adding features post-deployment. Blockchain technology can be integrated with update mechanisms to provide tamper-proof and auditable firmware update logs, particularly important in edge and IoT SSDs where physical security is limited [26], [27].

#### VI. CASE STUDIES AND IMPLEMENTATION

### A. SoftSSD: High-Level Firmware Emulation

SoftSSD is a high-level SSD firmware emulator implemented within the QEMU virtualization platform, designed to facilitate rapid development and testing of SSD firmware features without the need for physical hardware [28]. By abstracting the NAND flash interface, SoftSSD models the firmware stack including key components such as metadata journaling, wear-leveling, garbage collection, and command queuing. This approach enables developers to quickly iterate firmware logic, validate algorithms, and debug performance issues in a con- trolled and reproducible software environment.

SoftSSD's modular design supports flexible configuration of flash memory parameters and workload types, making it highly suitable for academic research and firmware prototyping. Its ability to simulate detailed firmware behavior accelerates development cycles and reduces the costs associated with hardware testing. However, since it operates above the NAND interface, it may not capture low-level flash hardware idiosyncrasies, which must be addressed in later hardware-based testing.

# B. FEMU: Flash Emulation Framework for Firmware Performance Testing

FEMU (Flash Emulation Framework) is an opensource SSD firmware emulator built on QEMU, designed for de-tailed performance testing and functional validation of SSD firmware. Unlike traditional simulators, FEMU provides realistic emulation of NAND flash behavior including latency variation, program/erase cycles, and error patterns, allowing evaluation of firmware techniques under conditions that closely mimic real hardware. FEMU supports integration of custom firmware components such as FTL algorithms, garbage collection policies, and wear-leveling schemes, enabling re-searchers to benchmark their solutions with real workload traces [29]. Its plugin-based architecture allows the addition of new flash models and firmware extensions without major rework. FEMU's precise timing and fault injection capabilities make it particularly valuable for studying firmware resilience and optimization strategies. While FEMU requires more setup and computational resources than SoftSSD, it offers greater fidelity and is a critical tool for bridging the gap between software emulation and physical hardware testing in firmware development workflows.

### VII. CONCLUSION

This review has outlined the critical role and evolving complexity of SSD firmware, highlighting key advancements in firmware architecture, core functionalities, and practical implementations. SSD firmware has evolved from simple address translators to complex control systems central to device performance, reliability, and security. Innovations in FTL design, garbage collection, wear leveling, error correction, and secure update mechanisms ensure

SSDs can meet the increasing demands of diverse applications. Simulation platforms and AI-driven techniques offer promising avenues for future firmware development. While SoftSSD and FEMU support firmware-level emulation with a focus on architectural design, NVM simulator [30] provides a more detailed, circuit-level NAND flash simulation, allowing developers to model timing and power behavior with high accuracy.

Despite these advances, challenges such as scaling firmware for new NAND types, managing update reliability, and ensuring robust security remain. Addressing these will require continued collaboration between academia and industry, with an emphasis on modular firmware designs, enhanced validation frameworks, and adaptive management techniques.

Future research should focus on refining firmware scalability and resilience, integrating computational storage capabilities, and developing standardized frameworks for secure and seamless firmware updates. Such efforts will be essential to meet the increasing complexity of storage systems and unlock the full potential of emerging SSD technologies.

### REFERENCES

- [1] S. H. Lim, S. Park, and K. Kim, "A Novel FTL Design for Improving SSD Performance and Endurance," IEEE Transactions on Consumer Electronics, vol. 62, no. 3, pp. 254-262, Aug. 2016.

- [2] J. Lee and K. Choi, "Firmware Optimizations for High Performance SSDs in Data Centers," Proc. IEEE International Conference on Cloud Computing, 2020, pp. 123-130.

- [3] Y. Cai et al., "Error Patterns in MLC NAND Flash Memory: Measurement, Characterization, and Analysis," Design, Automation & Test in Europe Conference (DATE), 2012, pp. 1343-1348.

- [4] A. S. K. Pathan, "Solid State Drives: An Overview of Architecture and Challenges," Journal of Computer Science and Technology, vol. 33, no. 4, pp. 727–740, 2018.

- [5] M. Lee et al., "FEMU: A Flash Memory Emulator for Firmware Development," Proc. ACM Symposium on Operating Systems Principles, 2019, pp. 456–469.

- [6] R. Kim, "Robustness Verification of SSD Firmware using Power-Fault Injection and Formal Methods," IEEE Transactions on Dependable and Secure Computing, vol. 17, no. 5, pp. 992–1005, 2020.

- [7] K. Zhang et al., "FlashSim: A Simulation Framework for SSD Firmware Research," IEEE International Symposium on Modeling, Analysis and Simulation of Computer and Telecommunication Systems (MASCOTS), 2014, pp. 71-80.

- [8] L. Xu and D. Li, "Advances in SSD Firmware Architectures," IEEE Access, vol. 8, pp. 145125–145138, 2020.

- [9] H. Yang et al., "Demand-based FTL with Adaptive Caching for NAND Flash Memory," IEEE Transactions on Computer-Aided Design, vol. 38, no. 8, pp. 1401-1412, Aug. 2019.

- [10] J. Park and S. Kim, "Performance and Reliability Enhancement Techniques for Modern SSD Firmware," IEEE Transactions on Circuits and Systems, vol. 67, no. 11, pp. 3987–4000, Nov. 2020.

- [11] B. Liu and Y. Cao, "Garbage Collection Policies for Reducing Write Amplification in SSDs," ACM Transactions on Storage, vol. 15, no. 2, 2019.

- [12] M. Wu et al., "Hot and Cold Data Separation for Flash Memory," IEEE Transactions on Computer-Aided Design, vol. 39, no. 4, pp. 760-773, April 2020.

- [13] K. Wang et al., "Embedded SSD Firmware: Design Challenges and Solutions," IEEE Embedded Systems Letters, vol. 11, no. 1, pp. 14-17, Mar. 2019.

- [14] Z. Zhou et al., "Lazy Garbage Collection for SSDs," IEEE Transactions on Computers, vol. 69, no. 5, pp. 682-695, May 2020.

- [15] J. Kim and H. Park, "NVMe Firmware Enhancements for SSDs in Data Centers," IEEE Transactions on Parallel and Distributed Systems, vol. 31, no. 6, pp. 1401-1414, June 2020

- [16] C. Lin and F. Chang, "I/O Scheduling and Parallelism Exploitation in SSD Firmware," Proc. IEEE Symposium on Mass Storage Systems and Technologies, 2019, pp. 1-10.

- [17] D. Patel et al., "AI-driven Firmware Management for Next Generation SSDs," IEEE Transactions on Artificial Intelligence, vol. 2, no. 4, pp. 265-275, Dec. 2021.

- [18] T. Huang and S. Chien, "Power-Loss Protection Techniques for SSD Firmware," IEEE Transactions on Industrial Electronics, vol. 66, no. 11, pp. 8647-8655, Nov. 2019.

- [19] H. Lee et al., "Zoned Namespace SSD Firmware Design for Endurance and Performance," IEEE Transactions on Storage, vol. 8, no. 3, 2022.

- [20] M. Singh and A. Kumar, "Secure Firmware Updates Using Blockchain for IoT Storage Devices," IEEE

- Transactions on Information Forensics and Security, vol. 15, pp. 2346-2359, 2020.

- [21] R. Jain et al., "SSD Firmware Security: Challenges and Solutions," IEEE Security & Privacy, vol. 18, no. 2, pp. 36-45, March-April 2020.

- [22] S. Zhang et al., "AutoFTL: Adaptive Firmware for Flash Memory Storage," IEEE Transactions on Computers, vol. 69, no. 8, pp. 1154-1166, Aug. 2020.

- [23] J. Marquez, A. Jaleel, M. Upton, and C. Wilkerson, "WARM: A write hotness aware retention management," in \*Proc. USENIX Conf. on File and Storage Technologies (FAST)\*, 2015.

- [24] K. Im, S. Park, and J. Choi, "A new error correction method using concatenated BCH and LDPC for NAND flash memory," \*IEEE Transactions on Dependable and Secure Computing\*, vol. 18, no. 3, pp.1234–1245, 2021.

- [25] J. Li and X. Zhang, "Efficient LDPC implementation with hardware-software co-design," \*IEEE Transactions on Computers\*, vol. 68, no. 9, pp. 1362–1375, 2019.

- [26] Samsung Electronics, "Samsung SSD 970 PRO Data Sheet," 2022. [Online]. Available: https://semiconductor.samsung.com.

- [27] Intel, "Intel SSD DC Family: Power Loss Imminent (PLI) Protection," 2021. [Online]. Available: https://www.intel.com

- [28] J. Kim, H. Kim, J. Jeong, and J. Kim, "SoftSSD: A High-Level SSD Simulation Framework for Exploring Firmware Behavior," IEEE Computer Architecture Letters, vol. 16, no. 1, pp. 24–27, Jan.–June 2017, doi: 10.1109/LCA.2016.2633262.

- [29] J. Xu, H. Zhang, Y. Zhang, Y. Chen, and T. Li, "FEMU: A QEMU-based SSD Emulator with Microsecond-Scale Timing Accuracy," in Proceedings of the 2018 USENIX Annual Technical Conference (USENIX ATC 18), Boston, MA, USA, Jul. 2018, pp. 83–95.

- [30] M. Jung and M. Kandemir, "NVMSim: A Circuits-Level NAND Flash Memory Simulator," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 31, no. 8, pp. 1191–1204, Aug. 20