ISSN: 2320-2882

**IJCRT.ORG**

# INTERNATIONAL JOURNAL OF CREATIVE RESEARCH THOUGHTS (IJCRT)

An International Open Access, Peer-reviewed, Refereed Journal

# IMPLIMENTATION ON INTEGRATED SINGLE INPUT DUAL OUTPUT DC-DC BUCK-BOOST CONVERTER

## <sup>1</sup> ANITHA M, <sup>2</sup> VANITHA M

<sup>1</sup>PG Scholar, Department of EEE, <sup>2</sup>PG Scholar, Department of EEE Government College of Engineering, Salem, Tamil Nadu, India

*Abstract:* Power converters with DC-DC output are gaining more attention in the world of electronic research. The development of SIMO converters was necessary to meet changing voltage requirements. With an integrated dual output converter, boost and buck operations can be performed at the same time through a single input power source. A number of power switches are used to develop the integrated converter, as opposed to a conventional buck-boost converter. With the integrated single input dual output converter, both switches can be operated together and simultaneously to produce buck and boost voltages. Multiple outputs can be controlled with the PIC controller. We develop and test a hardware prototype for an integrated dual output converter.

Keywords- Converter with one input and two outputs integrated, single input dual output (SIDO)

#### I. INTRODUCTION

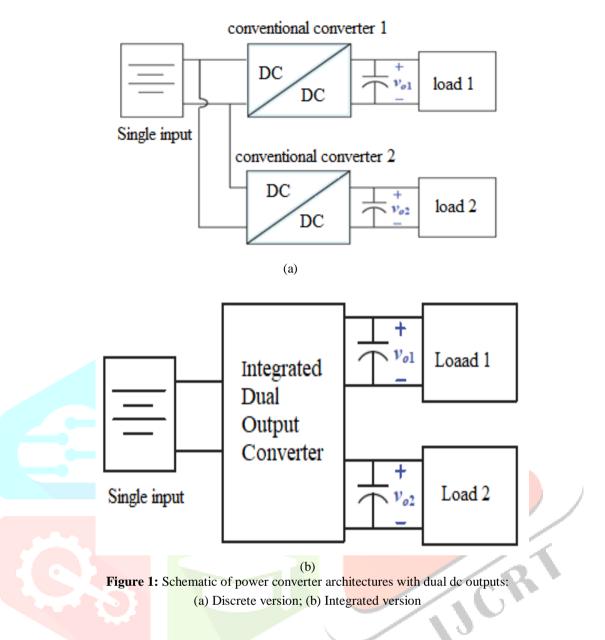

Single input dual output converters are increasing rapidly in number compared to conventional converters. In addition to electric vehicles, LED lamp devices, and HID lights, two output converters are commonly used in many other applications as well. Conventional SIMO converters are formed by interconnecting individual converters to a common input dc bus. In this case, the voltage requirements will vary according to the application SIMO dc to dc converters are attracting scientific attention because of their small size, reliable operation, and low cost. Because of this, SIMO DC-to-DC converters play an important role in industrial applications. DC-DC converters with multiple outputs can be designed very effectively with the help of power electronics. Power electronic converters are smaller and fit more comfortably in small spaces while still supplying enough power. By using appropriate PWM methods, it is also possible to reduce switching loss. Typically, DC-DC converters with several outputs use different DC-DC converters for each output. Figure 1 illustrates the single input multiple output architecture of a conventional dc-dc converter.

For some conventional DC-DC converters with multiple outputs, DC-DC converters with different output voltage requirements are used individually. A DC-DC converter with an isolated front end, transformer, and at least two switches at the rear end is called an isolated DC-DC converter. This system is bulkier and more complex since four switches and control drive circuitry are included. All the above components are required in a DC-DC converter. Therefore, the overall system becomes complex. Multiple-output DC-DC converters may be interspersed to get multiple outputs. Power density decreases when there are more switches and a transformer. Additionally, leakage inductance decreases transformer efficiency.

SIMO DC to DC converters have multiple outputs, but are based on an integrated architecture fig.1 (b). It is proposed here that a conventional SISO-type dc-dc converter can be reconstructed to form using a basic cell which consists of a switch, diode, inductor, and additional output, a SIDO style converter can be created. Due to lower component costs and fewer components, the dual output converter structure is compact.

Two switches are required to get a dual output from a conventional converter. When the two switches are turned on simultaneously, both buck and boost voltage are generated. There are three options for switching the converter. Choosing the ripple content of the inductor current and capacitor voltage can make passive components larger so as to achieve high efficiency. An input-output converter topology with single input and dual output is described in the paper. Simulation of the converter topology and development of hardware modelling are done with MATLAB/SIMULINK in this project. It is demonstrated how a prototype circuit was designed and the experimental results are substantiated the theory.

#### **II.** OPERATION

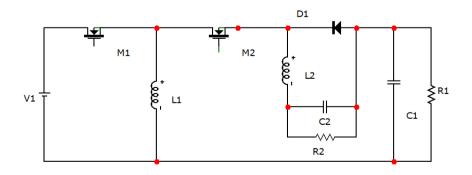

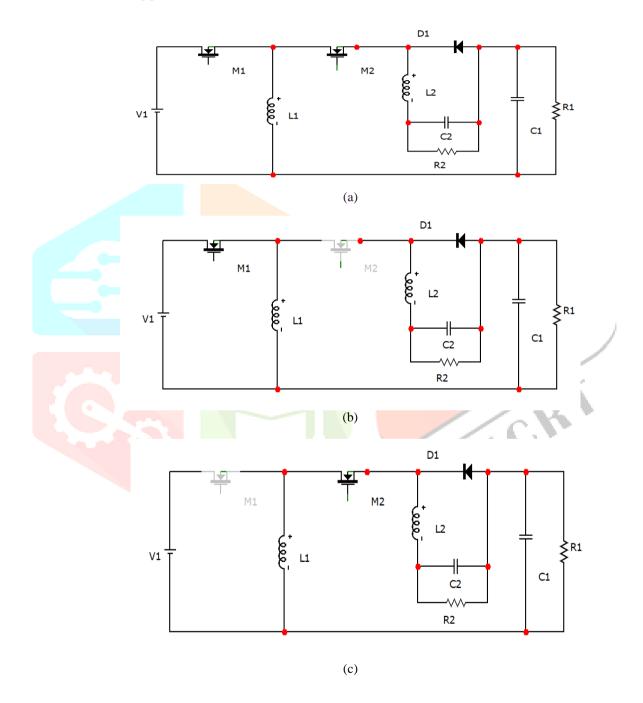

Circuit diagram of ISIDO converter a topology for an integrated single-input dual-output power converter is shown in fig .2, among the components are a single DC supply, two interconnected switches, two capacitors, two inductors, and one diode. Similar dynamic characteristics exist in this converter and conventional converters. High switching frequencies are possible with this converter. A dual output converter is capable of three different modes, and the equivalent circuits for each are shown in Figure 3.

#### www.ijcrt.org

### Interval 1 ( $t_o - t_1$ ):

In this circuit, both switches  $S_1$  and  $S_2$  are ON in advance of time  $t_o$ , and diode  $D_1$  is biased in the opposite direction. During  $t_o$ ,  $D_1$  has a forward bias, and  $S_2$  has been turned off. A voltage across the inductors  $L_1$  and  $L_2$  is generated by  $V_{in}$  and  $V_{o1}$ - $V_{o2}$  respectively during this interval.

#### Interval 2 ( $t_1 - t_2$ ):

At  $t_1$ , when  $S_1$  is turned off,  $IL_1+IL_2$  commute with current  $IL_1$  from the parasitic diode of  $S_2$ . As long as  $S_2$  is ON during this interval, this acts as an asynchronous rectifier switch. The inductors  $IL_1$ ,  $IL_2$ , are de-energized as a consequence of  $V_{in}$ , and  $-V_{o2}$ .

#### Interval 3 $(t_2 - t_3)$ :

A reverse bias is applied to  $D_1$  and  $S_1$  is turned on at  $t_2$ . By energizing Inductor L1 by Vo1, Inductor L2 by -Vo1. At t3, s2 is turned off and a switching period ends.

Figure 3: Typical operating circuits for the SIDO Buck-Boost converter in CCM: (a) interval 1, (b) interval 2, and (c) interval 3.

#### **III. DESIGN EQUATION**

For integrated dual output converters, inductor and capacitor designs are based on the conventional converter analysis. Following these steps will allow you to calculate the duty ratio of the switches. The inductor  $L_1$

| $V_{in}D_1 + (V_{in} - V_{01})(1 - D_1) = 0$                                                   | (1) |

|------------------------------------------------------------------------------------------------|-----|

| $\frac{V_{o1}}{V_{in}} = \frac{D_1}{1 - D_1}$                                                  | (2) |

| Similarly, for the inductor $L_2$<br>$(V_{o1} - V_{o2})(D_1 + D_2 - 1) - V_{o2} (1 - D_2) = 0$ | (3) |

| $\frac{V_{o2}}{V_{o1}} = \frac{D_1 + D_2 - 1}{D_1}$                                            |     |

| $\frac{V_{o2}}{V_{in}} = \frac{D_1 + D_2 - 1}{1 - D_1}$                                        | (4) |

Where,

$V_{o1}$  = Boost Converter Load Voltage  $V_{o2}$  = Buck Converter Load Voltage  $V_{in}$  = Supply Voltage of IDOC Converter  $D_1$  = Boost Converter Duty cycle  $D_2$  = Buck Converter Duty cycle

Boost and buck duty cycles (d1 and d2) are added together to calculate the duty ratio. If this duty ratio value is equal to unity, there must be a difference. Here are the steps that can be taken to express the power balance equation.

| $V_{in} * I_{in} = V_{o1} * I_{o1} + V_{o2} * I_{o2}$                                    |                                   | (5)      |

|------------------------------------------------------------------------------------------|-----------------------------------|----------|

| Where,                                                                                   |                                   |          |

| I <sub>01</sub> = Boost Converter Load current                                           |                                   |          |

| I <sub>02</sub> = Buck Converter Load current                                            |                                   |          |

| I <sub>in</sub> = Input Source current                                                   |                                   |          |

|                                                                                          |                                   |          |

| The following expressions should g                                                       | uide the selection of passive com | ponents: |

| $L_1 = \frac{V_{01}(1 - D_{S1})}{0.2 \times I_{L1Max} \times F}$                         |                                   | (6)      |

| $L_2 = \frac{V_{o2}(D_{S1} + D_{S2} - 1)}{0.2 \times I_{L2Max} \times F}$                |                                   | (7)      |

| $L_1 = \frac{90 (1 - 0.75)}{0.2 \times 1.8 \times 100 \times 10^3} = 625 \ \mu \text{H}$ |                                   |          |

| $L_2 = \frac{12(0.75+0.35-1)}{0.2\times2.5\times100\times10^3} = 24\mu\mathrm{H}$        |                                   |          |

| $C_1 = \frac{I_{01} D_1}{F \times \Delta V_{01}}$                                        |                                   | (8)      |

| $C_2 = \frac{I_{02} D_2}{F \times \Delta V_{02}}$                                        |                                   | (9)      |

| $C_1 = \frac{1.8 \times 0.75}{100 \times 10^3 \times 0.9} = 15 \mu F$                    |                                   |          |

| $C_2 = \frac{2.5 \times 0.35}{100 \times 10^3 \times 0.16} = 72 \mu \mathrm{F}$          |                                   |          |

Where,

A buck converter consists of capacitors and inductors called C2 and L2, respectively This converter can be configured with boost voltages of 90V and buck voltages of 12V with duties of 0.77 and 0.35, respectively. A time delay separates the two switching pulses

#### Time delay=0.5\* D<sub>2</sub>

Voltage bucking and boost are affected by duty cycle. As a result, the switch stress is reduced in IDOC converters both for boost and buck switches. There are equal currents in the inductors L1 and L2 as well as in the output resistors Io1 and Io2. For L1 and L2, the inductor current is equal to the average output currents Io1 and Io2The maximum average inductor currents, IL1

ww.ijcrt.org © 2022 IJCRT | Volume 10, Issue 6 June 2022 | ISSN: 2320-2882 max, and IL2 max, are obtained in this case. The required inductances of  $L_1 - L_2$  are calculated assuming that the ripple of the inductor current is less than 20% of the maximum inductor current.

| RATING                    |

|---------------------------|

| 30 V                      |

| 90V                       |

| 12V                       |

| 1.8 A                     |

| 2.5 A                     |

| 100kHZ                    |

| 0.75                      |

| 0.35                      |

| 625µH                     |

| 24µH                      |

| 40μΗ                      |

| 10µH                      |

| P = 0.00034,I=1,D=0.00001 |

| P = 0.00034,I=2,D=0.00001 |

|                           |

#### TABLE I. DESIGN PARAMETERS SPECIFICATION OF ISIDO CONVERTER

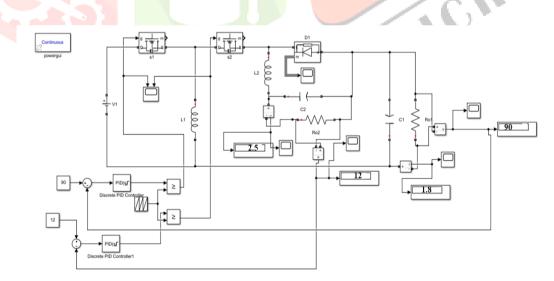

#### IV. MATLAB SIMULATION OF THE CONVERTER AND SIMULATION

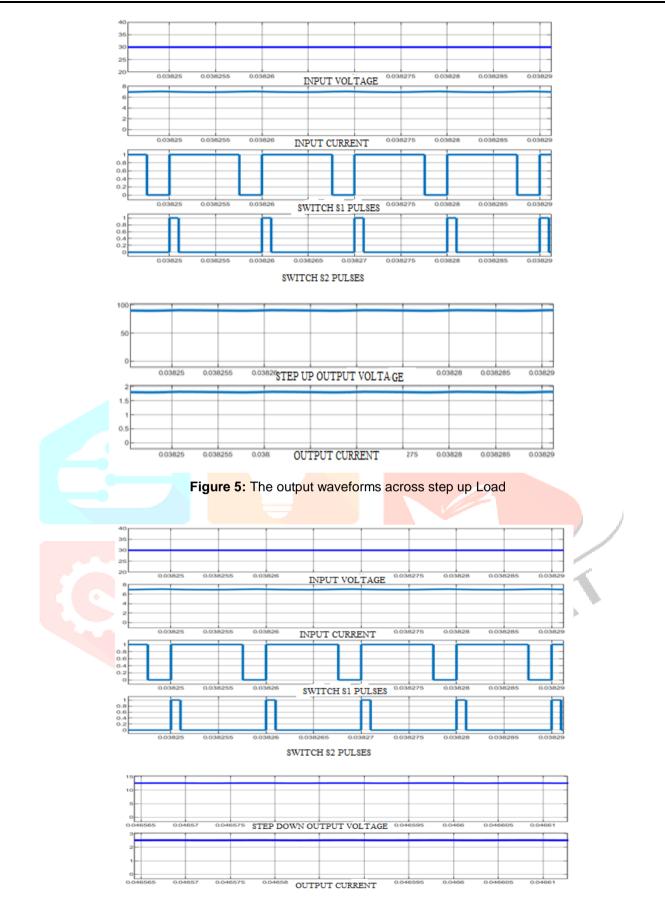

To simulate the circuit, MATLAB/SIMULLINK are used. A buck-boost converter and an interleaved converter is presented in Table I. The design of a DC-DC converter is shown simulated in Mat lab fig 4. An analysis of the simulation results of Integrated Dual Output Converters (IDOC) is performed. Fig. 4. In Fig. 5 we see the simulated results for the boost part of the IDOC converter, while in Fig.6 we see the buck part of the IDOC converter. Figure 4 shows how 30V input voltage is boosted to 90V to obtain a step down voltage of 12V when duty cycles of 0.75 and 0.35, respectively, are applied to the switch S1 and S2. It is observed that the source current is 6.42A whereas the load currents of boost and buck part of IDOC are 1.8A and 2.5 A respectively. Parts for the step up and step down motions have load resistances of 50 ohm and 5 ohm, respectively.

Figure 4: Mat LAB / Simulink circuit diagram of integrated single Input dual output dc-dc Buck-Boost converter

Figure 6: The output waveforms across step down Load

#### **V. HARDWARE RESULT**

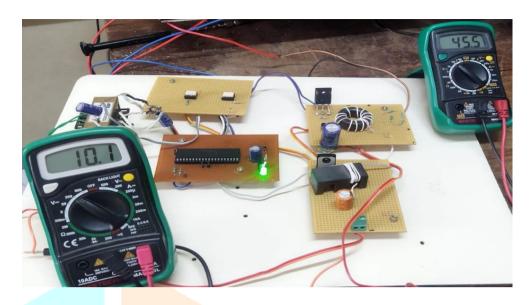

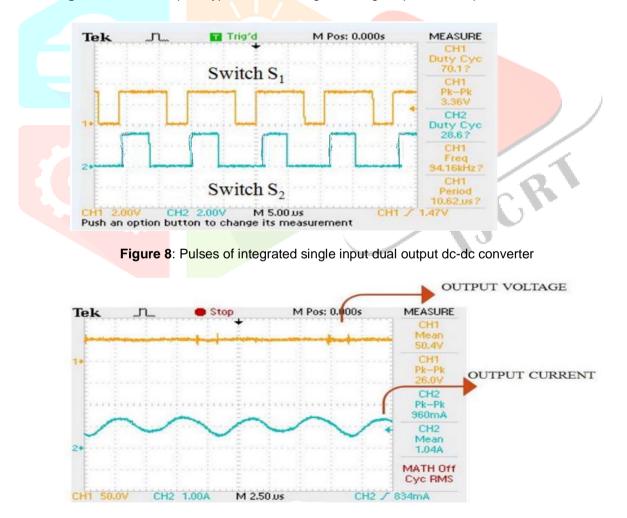

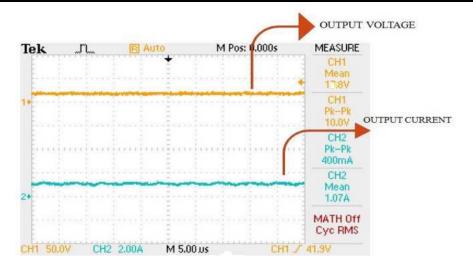

As shown in Fig.7, we have set up an experimental IDOC converter. The output waveforms of both step up and step down operations are captured for the shoot through switching frequency of 100 kHz coupled with duty ratios of 0.70 and 0.28.

Figure 7: Hardware prototype model of integrated single input dual output DC-DC converter

Figure 9: Step up output waveforms for integrated single input dual output dc-dc converter

Figure 9: Step down output waveforms for integrated single input dual output dc-dc converter

#### VI. CONCLUTION

We have presented a novel method of constructing topology synthesis from conventional SISO converters that can be utilized to produce a wide variety of integrated SIDO dc–dc converters. As a result of the reduced number of components used in the integrated SIDO Buck boost converter, the converters achieved a lower cost than conventional converters. Several components were used to construct this converter, such as two switches, a diode, two capacitors, and two inductors. In addition, switching losses were reduced as a result. The two output voltages are controlled by using two duty cycles of switches, which makes cross-regulation rejection effective Comparing the proposed SIDO Buck boost converter to a conventional one, Stresses will be increased, leading to increased conduction losses. A high-frequency converter can be realized using the proposed converter.

#### REFERENCES

- S. K. Rastogi, M. S. Rana and S. K. Mishra, "A Single-Input Multiple-Output Unity Power Factor Rectifier," in *IEEE Transactions on Power Electronics*, vol. 36, no. 9, pp. 10127-10141, Sept. 2021, doi: 10.1109/TPEL.2020.3045130

- [2] O. Ray, A. P. Josyula, S. Mishra and A. Joshi, "Integrated Dual-Output Converter," in IEEE Transactions on Industrial Electronics, vol. 62, no. 1, pp. 371-382, Jan. 2015, doi: 10.1109/TIE.2014.2327599

- [3] X. Liu, J. Xu, Z. Chen and N. Wang, "Single-Inductor Dual-Output Buck-Boost Power Factor Correction Converter," in IEEE Transactions on Industrial Electronics, vol. 62, no. 2, pp. 943-952, Feb. 2015, doi: 10.1109/TIE.2014.2334659.

- [4] A. Ganjavi, H. Ghoreishy and A. A. Ahmad, "A Novel Single-Input Dual-Output Three-Level DC-DC Converter," in IEEE Transactions on Industrial Electronics, vol. 65, no. 10, pp. 8101-8111, Oct. 2018, doi: 10.1109/TIE.2018.2807384.

- [5] G. Chen, Z. Jin, Y. Deng, X. He and X. Qing, "Principle and Topology Synthesis of Integrated Single-Input Dual-Output and Dual-Input Single-Output DC-DC Converters," in IEEE Transactions on Industrial Electronics, vol. 65, no. 5, pp. 3815-3825, May 2018, doi: 10.1109/TIE.2017.2760856.

- [6]M. Shang and H. Wang, "A ZVS integrated single-input-dual-output DC/DC Converter for high step-up applications," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), 2016, pp. 1-6, doi: 10.1109/ECCE.2016.7854810.

- [7]J. Kim, S. Choi, C. Kim and G. Moon, "A New Standby Structure Using Multi-Output Full-Bridge Converter Integrating Flyback Converter," in IEEE Transactions on Industrial Electronics, vol. 58, no. 10, pp. 4763-4767, Oct. 2011, doi: 10.1109/TIE.2011.2106101.

- [8]P. Shamsi and B. Fahimi, "Dynamic behavior of multiport power electronic interface under source/load disturbances", IEEE Trans. Ind. Electron., vol. 60, no. 10, pp. 4500-4511, Oct. 2013.

- [9]C. N. Onwuchekwa and A. Kwasinski, "A modified-time-sharing switching technique for multiple-input DC-DC converters", IEEE Trans. Power Electron., vol. 27, no. 11, pp. 4492-4502, Nov. 2012.

- [10]G. Chen, Z. Jin, Y. Deng, X. He and X. Qing, "Principle and Topology Synthesis of Integrated Single-Input Dual-Output and Dual-Input Single-Output DC–DC Converters," in IEEE Transactions on Industrial Electronics, vol. 65, no. 5, pp. 3815-3825, May 2018, doi: 10.1109/TIE.2017.2760856.