# TWO STAGE OPERATIONAL AMPLIFIER USING 90nm TECHNOLOGY

M.SATYANARAYANA<sup>1</sup> Dr. D.NAGESHWAR RAO<sup>2</sup>, K.ARAVINDKUMAR<sup>3</sup>, K.VAMSHIKRISHNA<sup>4</sup>, K.VINITHA<sup>5</sup> <sup>1</sup>ASSISTANT PROFESSOR OF ECE DEPARTMENT, TKR COLLEGE OF ENGINEERING AND TECHNOLOGY, HYDERABAD, INDIA

<sup>2</sup>HOD OF ECE, TKR COLLEGE OF ENGINEERING AND TECHNOLOGY, HYDERABAD, INDIA. <sup>3</sup>TKRCOLLEGE OF ENGINEERING AND TECHNOLOGY, ECE DEPARTMENT, HYDERABAD, INDIA. <sup>4</sup>TKRCOLLEGE OF ENGINEERING AND TECHNOLOGY, ECE DEPARTMENT, HYDERABAD, INDIA. <sup>5</sup>TKRCOLLEGE OF ENGINEERING AND TECHNOLOGY, ECE DEPARTMENT, HYDERABAD, INDIA.

*Abstract*— The design of high gain and power of analog components can be designed by using fully differential circuit concepts with the help of Operational Amplifiers (Op-Amps). The Op-Amp can be designed by providing the amplification of input voltages at two stages. The two stage Op-Amp features can be improved by providing the concepts like CS Amplifier, cascade etc. The Op-Amp design for high speed applications requires proper selection of biasing, logic style, and CS Amplifier as the technology is scaling down. This basic Op-Amp performance metrics can be improved by adding the CS Amplifier. The Op-Amps are designed for both with single operational amplifier and CS Amplifier with gain improvement using Cadence full custom design suite for 90nm technology.

Keywords— Single Stage Op-Amp, CS Amplifier, Mirror Pole , PMOS & NMOS of 90nm Technology.

#### I. INTRODUCTION

The design of high gain analog components can be designed by using fully differential circuit concepts with the help of Operational Amplifiers (Op-Amps). The Operational Amplifiers (Op amps) are one of the most widely used building blocks for analog and mixed signal systems. They are employed from dc bias applications to high speed amplifiers and filters. General purpose op amps can be used as buffers, summers, integrators, differentiators, comparators, negative impedance converters, and many other applications. While many digital circuits can be adapted to a smaller device level with a smaller power supply, most existing analog circuitry requires considerable change or even a redesign to meet the same constraints. With transistor length being scaled down to a few tens of nanometers, analog circuits are becoming increasingly more difficult to improve upon. The basic two stage Op-Amp can be designed by using MOS technology to meet the features and constraints. The basic Op-Amp features are gain, gain bandwidth, Slew rate, Common-Mode Rejection Ratio (CMRR), Power Supply, output-voltage swing, output resistance, offset etc. The open loop gain of Op-Amp for a particular technology cannot match with the bipolar based Op-Amps. This is due to small trans conductance of this devices as well as the gain reduction due to short channel effects that come into play for submicron processes. As a result, gain boosting schemes must be used to improve the gain. These gain enhancing methods often require more complicated circuit structures and higher power supply voltage, and may produce a limited output voltage swing. Hence multiple stage amplifiers may be used for higher gain analog circuit designs. But the multistage amplifiers generally are difficult to construct. However, most methods require more circuit area and more complex design than the dominant pole approach used in the classic op amp architecture. Special problems of integrated circuit amplifiers which include lack of large sized capacitors, parasitic coupling, and package parasitic and on/off chip load problems make the constructing more difficult than discrete component amplifiers. The main aim of this work is to design two stage op amp with CS Amplifier to improve the gain using 90nm technology and cadence full custom design suite. This paper is organized such that the section II gives general background and information of Op-Amp basic theory. The section III describes the design specifications, requirements and design methodology. The chapter IV gives the details of full custom design of op amp using Cadence tools and also describes the simulation results to demonstrate the functional verification and performance improvements. The conclusion is presented in section V followed by references.

#### II. BASIC THEORY OF OP-AMP

The Op Amp (Operational Amplifier) is a high gain, dc coupled amplifier designed to be used with negative feedback to precisely define a closed loop transfer function. The gain produced by the op amp is higher than the gain produced by normal amplifiers. Thus it is a high gain amplifier. The basic symbol of Op-Amp is shown in Figure 1. The op amp symbol has two input terminals, one is positive terminal and other is negative terminal, voltage supplies to op amp as +VDD, -VSS and one output terminal.

Figure 1: Symbol of Op-amp

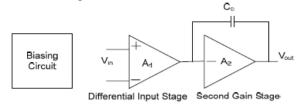

The basic block diagram of op-amp is shown in Figure 2.

Figure 2: Block diagram of op-amp

The op-amps can be designed by using either two stage topology or folded cascade topology by modifying the stage 1.stage-2 or at any portion of the basic op-amp topology. The selection of the topology is based on the required non functional parameters and features of op-amp.

#### III. DESIGN OF OP-AMP

The design of two stage op-amp can be done by using the following steps .

Step-1: Selection of the transistor logic style or logic family.

Step-2: Basic structure for the op-amp from the selected

Logic family.

Step-3: Selection of transistor in 90nm technology.

Step-4: Physical verification.

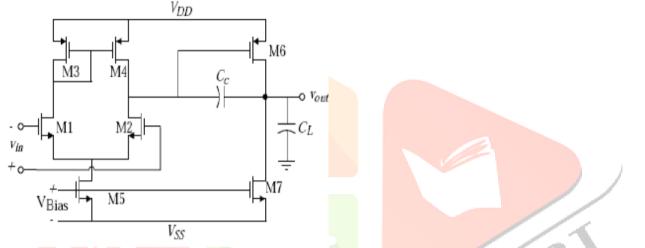

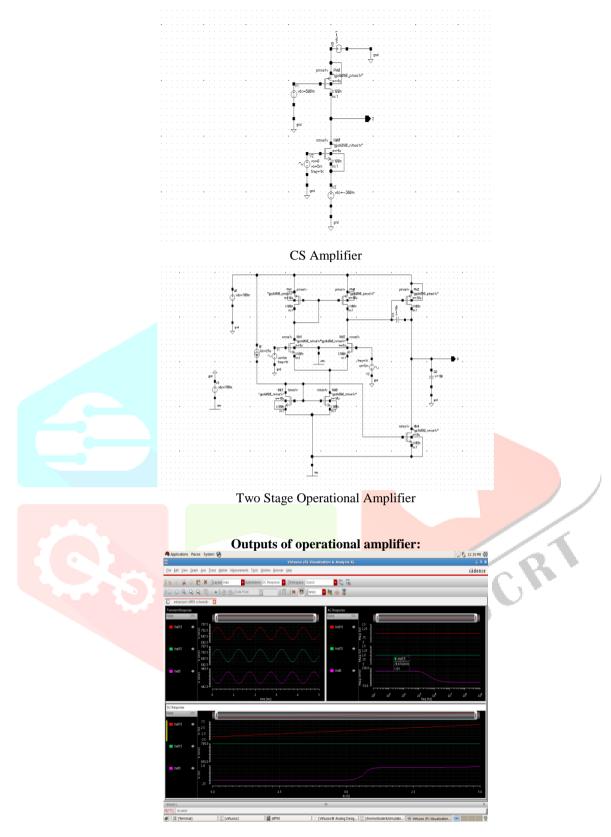

#### Figure-3 Two stage operational Amplifier

The input is a differential one for the current source, Transistors M5 and M7 are biasing transistors that ensure the circuit to operate always in saturation region. The V<sub>out (max)</sub> and the gain can be increased by adding extra parallel transistors to M6 transistors. The design of single stage op-amp and cs amplifier is used to improve the gain performance parameter of opamp. The M1, M2, M3 and M4 transistors provides the differential input pair circuitry and the capacitor Cc is used as first stage load capacitor. The parallel combination of M6,M7 ......Mn transistors of cs amplifier of Figure 3 is used to improve the gain performance parameter of opamp. C<sub>L</sub> is used as load capacitor for overall circuit

#### IV. FULL CUSTOM DESIGN OF OP-AMP

The designed op-amp has been simulated to find the different characteristics of the designed op-amp. The total design performed in Cadence tool. Different test benches have been created and extracted design has been then simulated with the parasitic values and compared with the schematic. Later in the chapter we also have compared the obtained parameters of the device through simulation to the specifications for the device.

| Design Action       | Tool Name                                  |  |

|---------------------|--------------------------------------------|--|

| Schematic entry     | Virtuoso schematic editor                  |  |

| Symbol creation     | Virtuoso Symbol editor                     |  |

| Simulation          | Virtuoso Analog Design<br>Environment tool |  |

| Layout, DRC         | Assura                                     |  |

| Layout Vs Schematic | LVS tool                                   |  |

| Targeted Technology | 90nm                                       |  |

Table1: Cadence tool mapping for Full custom design flow

### www.ijcrt.org

## Design Issues

Typical Design factors

- DC Gain (Av) Frequency Response

- Unity Gain Bandwidth Phase Margin

- Power Dissipation Load Capacitance

- Slew Rate

- Output Voltage Swing

- CMRR

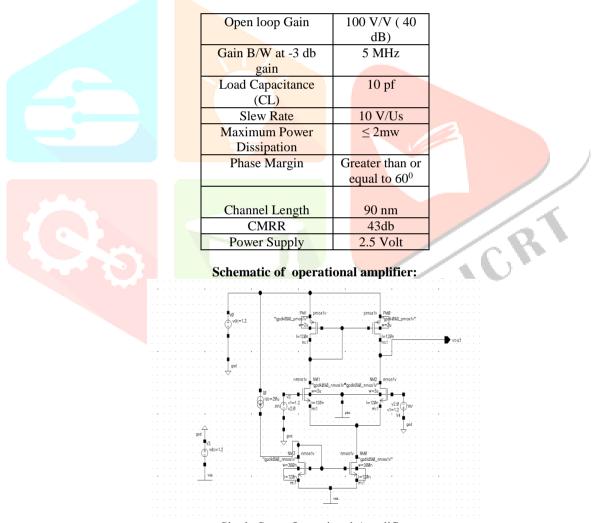

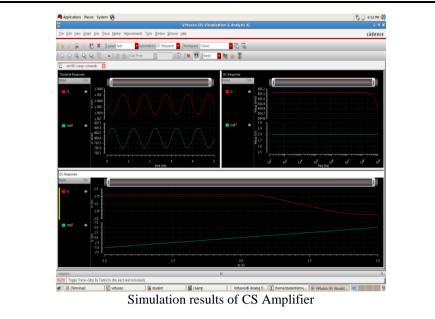

The design process involves the two major steps, the first is the conception of design ,and second one is optimization of design . The conception of the design has been accomplished by proposing an architecture to meet the given specifications. This step is normally done by using hand calculations in order to maintain the clear view point necessary for choices that must be made. Second step is to take the "first-cut" design and verify and optimize it. This is normally done by using Computer simulation and can include such influences as environmental or process variations. The full custom design of basic two stage op-amp using Cadence tools and 90nm is shown in Figure 4. This design is used for op-amp functional verification and the simulation result is shown in Figure 5. This design procedure assumes that the gain at dc (Av), unity gain bandwidth (GB), input common mode range (Vin(min) and Vin(max)), load capacitance (CL), slew rate (SR), settling time (Ts), output voltage swing (Vout(max) and Vout(min)) are given. Choose the smallest device length which will keep the channel modulation parameter constant and give good matching for current mirrors. Two stage OPAMP is designed for 90 nm technology for the following specifications :-

TABLE I DESIGN SPECIFICATION

Single Stage Operational Amplifier

Single Stage Operational Amplifier

| Applications Places System 😝                                                  |                                         | 🖏 🕢 6:38 PM 📢 |

|-------------------------------------------------------------------------------|-----------------------------------------|---------------|

| W Virtuoso (R) Visualiza                                                      | tion & Analysis XL                      |               |

| Elle Edit Werw Graph Avis Trace Marker Massurements Tools Window Browser Help |                                         | cädence       |

| 🛛 🥱 🦿 🙀 🗊 🛣 Ulayost (Auto 💽 Subwindows: DC Response 💽 (Workspace: Classic     |                                         |               |

| 🔾 🔾 🔍 🔍 🂐 🔹   🗶 💁 Data Point 💿 👘 🗍 🗐   🛤 🦻 (tamiy                             | 1 神 🍲 第                                 |               |

| mini38 2stagediffampi schematic 🚦                                             |                                         |               |

|                                                                               | AC Ressonse                             |               |

|                                                                               | Aout • 25.0                             |               |

|                                                                               | Non Siso                                |               |

|                                                                               | 3.0 g                                   |               |

| • § 25                                                                        | ■ //1 ◆ 215 ]                           |               |

| ≥ 25<br>                                                                      | W 25                                    |               |

| M2 • 15<br>S 25                                                               | ₩2 • 15<br>∑115                         |               |

| ₹ 25 j                                                                        | 1 2 2 4 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |               |

| -75 *                                                                         | ىم يەت يەت يەت يەت                      | 10 10         |

| time (m)                                                                      | 10° 10° 10° 10° 10° 10° 10° 10°         |               |

| DC Response Vis                                                               |                                         |               |

| Anat o 3                                                                      |                                         |               |

| <pre>\$1</pre>                                                                |                                         |               |

| 3                                                                             |                                         |               |

| δ <sup>25</sup><br>δ <sup>25</sup>                                            |                                         |               |

| > 35                                                                          |                                         |               |

| ■ M2 ● 10<br>S = 10<br>S = 10                                                 |                                         |               |

| 5 00 1<br>.1 0                                                                |                                         |               |

| -5.0 -2.5                                                                     | 00 25 dcfs                              |               |

| Induse L:                                                                     | de (0)                                  |               |

| 6(13) Toggle Trace->Ship By Family to ship each leaf individually             | и.                                      |               |

| 🜒 📓 [Terminal] 🛛 [ [ [virtuoso] ] 📓 2staged#ampl 🕺 Virtuoso@ Anaio [ ] Anor   |                                         | 9             |

| Simulation results of two                                                     | stage operational amplifi               | er            |

|                                                                               |                                         |               |

|                                                                               |                                         |               |

| V.CONC                                                                        | LUSIONS                                 |               |

The amplifier presented in this paper operates in saturation mode and regulates its bias current. When a signal is applied the current in the amplifier increases so that these amplifiers have very high driving current. The op-amp has low power as well as low voltage. Its slew rate is higher than reported. The unity gain bandwidth is obtained 5MHz. The two stage op amp circuit is designed for simple compensated features using 90nm technology with L=100nm and achieved a gain of 30 db. This simple op-amp design can be improved in performance by adding gain improvement circuitry.

#### REFERENCES

1] Vikas Sharma ,Anshul Jain, "Design of two Stage High Gain Opamp", Indian Journal of Research,Vol.2, pp-170-172,March 2013

2] D. Nageshwarrao, k. Suresh kumar, Y. Rajasree rao, G. Jyothi, implementation and simulation of CMOS two stage operational amplifier International Journal of Advances in Engineering & Technology, Jan. 2013.

3] Priyanka Kakoty, Design of a high frequency low voltage CMOS operational amplifier International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.1, March 2011.

4] P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, "Analysis and Design of Analog Integrated Circuits", 4th edition, New York: Wiley, pp. 644–645, (2001).Google Scholar

5] Hoi Lee and Philip K. T. Mok, "Active-Feedback Frequency-Compensation Technique for Low-Power Multistage Amplifiers", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, pp. 511–520, (MARCH 2003). Google Scholar

6] Mohammad Yavari, Student Member, IEEE, Nima Maghari, and Omid Shoaei, "An Accurate Analysis of Slew Rate for Two-Stage CMOS Opamps", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 52, NO. 3, pp. 164–167, (MARCH 2005). Google Scholar 7] Aldo Pena Perez, Nithin Kumar Y.B., Edoardo Bonizzoni, and Franco Maloberti, "Gain Enhancement in Two Stage Operational Amplifiers", IEEE, pp. 2485–2488, (2009).

PERFORMANCE IN IMAGE TRANSMISSION WITH OFDM", IJAICT Volume -1, Issue-1, May 2014. ICMAEM-2017 IOP PublishingIOP Conf. Series: Materials Science and Engineering 225(2017) 012217 doi:10.1088/1757-899X/225/1/012217

[13] Mr.P.Ratna Bhaskar, K.Mounika," Implementation of OFDM System For Image Transmission", International Journal on Recent and Innovation Trends in Computing and Communication ISSN: 2321-8169 Volume: 3 Issue: 5 3187 – 3191.

[14] Shadbhawana Jain and Shailendra Yadav," Image Transmission Using 64-QAM Modulation Technique in Digital Communication System", International Journal of Advanced Research in Computer Engineering & Technology (IJARCET) Volume 4 Issue 12

#### VI.AUTHOURS BIODATA

**M.SATYANARAYANA**, received his B.Tech degree in Electronics and Communication Engineering from Jawaharlal Nehru technological University in 2009, and he completed his M.Tech from Jawaharlal Nehru technological University in 2013. He is working as Assistant professor in TKR College of Engineering and technology, Hyd.

**Dr.D. Nageshwar Rao** received the B.E degree in Electronics Engineering from Shyamlal college of Engineering, SRTMU Nanded, in 1999 and M.Tech with specialization DSCE from J.N.T.U College of Engineering, JNTU HYD, in 2004. He completed Ph.D at GITAM University, Vishakapatnam in 2014. His doctoral research is directed towards the design of a low voltage, low power VLSI analog circuits. His area of research is Low power VLSI, Image Processing & Video Processing. Presently he is working as Professor in TKR College of Engineering & Technology, Meerpet, Hyd.

**K.ARAVIND KUMAR** studying B.Tech degree in Electronics and Communication Engineering from Jawaharlal Nehru technological University for the academic year 2014-18.

**K.VAMSHI KRISHNA** studying B.Tech degree in Electronics and Communication Engineering from Jawaharlal Nehru technological University for the academic year 2014-18.

**K.VINITHA** studying B.Tech degree in Electronics and Communication Engineering from Jawaharlal Nehru technological University for the academic year 2014-18.