# A New Technique to Select Multi Level Inverter

Nikhil Bodele M.Tech Student Department of Electrical Engineering TGPCET, Nagpur, India Dr. Hari Kumar Naidu Head Of Department Department of Electrical Engineering TGPCET, Nagpur, India Vaishali Pawade Assistant Professor Department of Electrical Engineering TGPCET, Nagpur, India

Abstract— In this paper, the different level inverters like five level, seven level and nine level inverters are compared. Inverters are needed to convert the direct current electricity produced by the array of DC system batteries used in various utilities like battery driven electric vehicles, PV cells in solar rooftops, variable frequency drive, Air conditioning, HVDC power transmission, Uninterruptable power supplies application etc into alternating current electricity required for loads. For the making the process of conversion more lossless and efficient various Multilevel Inverter techniques are used in applications where high power efficient conversion is required which in turn enhances the life of the utility. Based on this, three MLI techniques are selected for which an additional comparative analysis involving various level controls is conducted. Therefore, at the end of this paper, 5-level multilevel inverter's simulation output, 7-level multilevel inverter output and 9-level multilevel inverter output will be compared, focusing on power factor, total harmonic distortion (THD), and its efficiency. Hence, the better level of multilevel inverter will be concluded.

## I. Introduction

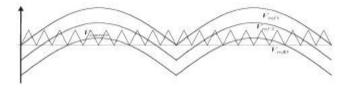

Nowadays, the use of MLI in power system have been increasing widely. Crucial with these demands, many researchers or designers have been struggling to find the most economic and reliable controller to meet these demands. The idea to have a control system in dc-ac converter is to ensure desired voltage output can be produced efficiently as compared to conventional rectification. The usage of electronic equipments is increasing rapidly in the daily life according to consumer or industrial needs. All these electronic equipments have power supplies that obtain required energy from utility grid [1-2]. And as the conventional sources of power are on the verge of extinction everyone is now turning their heads towards the non-conventional source of energy This non-conventional way always creates DC power and as our equipment's are made to work on AC current generally the use of inverter comes into effect. But these converter being a single level only they converts the DC energy to AC energy but with a loss of power in transition in the waveform pattern This causes current and voltage distortions that creates harmonics of different orders which in turn affects other equipment's connected to the same power line, thus, lowering the capability of the power source[3-4]. In order to overcome these problems, For DC-to-AC converter, multilevel inverter is a good choice for PV system, e-vehicles, variable frequency drive, Air conditioning, HVDC power transmission, Uninterruptable power supplies application. This is because it provides quite a lot of advantages. The biggest advantage of using various level MLI's is the waveform gets nearly

sinusoidal as we increase the number of levels with the effective reduction in harmonics. Therefore, at the end of this paper, 5-level multilevel inverter's simulation output, 7-level multilevel inverter output and 9-level multilevel inverter output will be compared , focusing on power factor, total harmonic distortion (THD), and its efficiency. Hence, the better level of multilevel inverter will be concluded. There are three types of conventional multilevel inverter topologies: neutral point clamped (NPC), flying capacitor (FC) and cascaded H-bridge multilevel inverter [2]. From the three above MLI topologies, cascaded H-bridge is more popular due to its simplicity in control, modular structure and no need of extra capacitor and diode. Cascaded H-bridge MLI can be divided in two categories: symmetrical and asymmetrical topology. In symmetrical topology all unit will have same value of dc voltage sources. In asymmetric topology different unit will have different value of dc voltage sources, binary or trinary depending on requirement. By using different voltage sources and increasing the magnitude of dc voltage sources, more level can be generated in output voltage. Therefore, asymmetrical multilevel inverters generate higher number of level in output voltage using less number of power electronic devices as compared to the symmetrical multilevel inverter.

## II. THEORY

## A. 5-level Multilevel Inverter

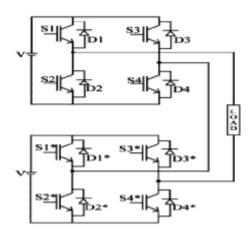

For 5-level inverter, the topology is presented in Figure 1. This topology consists of a full-bridge inverter, an auxiliary circuit (comprises of one switching element and four diodes) and two capacitors as voltage divider. The multilevel inverter is connected after the dc power supply. The main point of the auxiliary circuit is to generate half level dc supply voltage [3]. It also reduced the layout complexity compared to other multilevel inverter topology such as flying-capacitor topology, diode-clamped topology and hybrid topology, and these topologies can be studied in various papers such as in [4] and in [5]. The operations of the new topology were presented in literature [3], [6] and [7]. The output voltage levels according to the switch on-off conditions were tabulated in Table I. The switch in auxiliary circuit must be properly switched considering the direction of the load current.

Fig. 1(a) Topology of five level Multilevel Inverter.

TABLE I. Switching Scheme for five level Multilevel Inverter

| Voltage (Vo)       | <b>S</b> 1 | S2 | <b>S</b> 3 | S4 | S5 | S6 | <b>S</b> 7 | <b>S</b> 8 |    |

|--------------------|------------|----|------------|----|----|----|------------|------------|----|

| 0                  | 0          | 1  | 0          | 1  | 1  | 0  | 1          | 0          | ]  |

| $V_{dc}$           | 1          | 0  | 0          | 1  | 0  | 1  | 0          | 1          |    |

| $2 V_{dc}$         | 1          | 1  | 0          | 0  | 1  | 1  | 0          | 0          | 23 |

| - V <sub>dc</sub>  | 0          | 1  | 0          | 1  | 1  | 0  | 0          | 1          |    |

| -2 V <sub>dc</sub> | 0          | 0  | 1          | 1  | 0  | 0  | 1          | 1          |    |

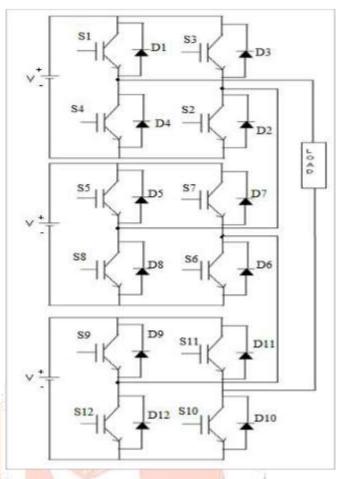

## B. 7-level Multilevel Inverter

The topology of 7-level inverter is similar to 5-level topology, only the auxiliary circuit now was added with an additional circuit. In general, 7-level inverter consists of a fullbridge inverter, two bidirectional switches (the auxiliary circuit), and three capacitors as voltage divider illustrated in Figure 2. To ensure that the power flows from the PV arrays to the grid, high dc bus voltages are necessary. LCL filter is used to filter the current to be injected into the utility grid. Seven output voltage level can be achieved when the switching signal for the IGBTs in the topology were done properly. The required seven levels of output voltage are generated, and the operation was explained in literature [8]. The switching combinations that generated the seven output voltage levels tabulated in Table II

Fig. 2(a) Topology of seven level Multilevel Inverter.

Table II. Switching Scheme for seven level Multilevel Inverter.

| Voltage (Vo)      | 81 | S2 | \$3 | \$4 | 85 | 86 | \$7 | \$8 | \$9 | S10 | S11 | S12 |

|-------------------|----|----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|

| 0                 | 0  | 1  | 0   | 1   | 0  | 1  | 0   | 1   | 0   | 1   | 0   | 1   |

| $V_{de}$          | 1  | 1  | 0   | 0   | 0  | 1  | 0   | 1   | 0   | 1   | 0   | 1   |

| $2V_{de}$         | 1  | 1  | 0   | 0   | 1  | 1  | 0   | 0   | 0   | 1   | 0   | 1   |

| 3V <sub>dc</sub>  | 1  | 1  | 0   | 0   | 1  | 1  | 0   | 0   | 1   | 1   | 0   | 0   |

| -V <sub>dc</sub>  | 0  | 1  | 0   | 1   | 0  | 1  | 0   | 1   | 1   | 1   | 0   | 0   |

| -2V <sub>60</sub> | 0  | 1  | 0   | 1   | 0  | 0  | 1   | 1   | 0   | 0   | 1   | 1   |

| -3V#              | 0  | 0  | -1  | 1   | 0  | 0  | 1   | 1   | 0   | 0   | 1   | 1   |

#### C. 9-level Multilevel Inverter

The topology of 9-level inverter is similar to 5-level topology, only the auxiliary circuit now was added with an additional circuit. In general, 7-level inverter consists of a fullbridge inverter, two bidirectional switches (the auxiliary circuit), and three capacitors as voltage divider illustrated in Figure 2. To ensure that the power flows from the PV arrays to the grid, high dc bus voltages are necessary. LCL filter is used to filter the current to be injected into the utility grid. Seven output voltage level can be achieved when the switching signal for the IGBTs in the topology were done properly. The required seven levels of output voltage are generated, and the operation was explained in literature [8]. The switching combinations that generated the seven output voltage levels tabulated in Table II

Fig. 3(a) Topology of nine level Multilevel Inverter.

| Table III. Switching | Scheme fo | r nine level | Multilevel Inverter. |

|----------------------|-----------|--------------|----------------------|

|                      |           |              |                      |

| Output voltage (Vo) | 51  | 82 | 53  | -54 | - 55 | -86 | \$7 | 58  | 59 | 510 | 511  | 812 | \$13 | \$14 | \$15 | \$16 |

|---------------------|-----|----|-----|-----|------|-----|-----|-----|----|-----|------|-----|------|------|------|------|

| 0                   | 0   | 1  | 0.  | 1   | 0    | -1  | 0   | T.  | 0  | 1   | .0   | 1   | 0    | 110  | 0    | 1    |

| V.                  | 1   | 1  | 0   | -0  | 0    | 1   | 0   | 1   | 0  | 1   | -0   | 1   | 0    | 1    | - 0  | 1    |

| 2V <sub>de</sub>    | 1   | 1. | 0   | .0  | 1    | -1  | - 0 | -0  | -0 | 1   | -0   | 1.  | 0    | 1    | 0.1  | -1   |

| 3V.#                | 1   | 1  | 0   | 0.  | 1    | 1   | . 0 | . 0 | 1  | 1   | . 0  | 0   | 0    | 1    | 0    | 1    |

| $4V_{de}$           | 1   | 1  | 0.  | 0   | 1.   | 1   | 0   | .0  | 1  | 1   | 0    | 0   | 1    | 1    | 0.1  | .0   |

| -V <sub>#</sub>     | -0  | 1  | - 0 | 1   | -0   | -1  | - 0 | 1   | -0 | 1   | ÷ 0. | 1   | - 0  |      | 1    | 11   |

| -2V <sub>ab</sub>   | 0   | 1  | 0   | 1   | 0    | 1   | .0  | 1   | -0 | 0   | 1    | 1   | 0    | 0.00 | 1    | 1    |

| -SV <sub>ab</sub>   | 0   | 1  | 0   | 1   | -0   | .0  | 1   | 1   | 0  | 0   | 1    | 1   | 0    | - 6  | 1    | 1    |

| -4V <sub>ab</sub>   | -07 | 0  | 1   | 1   | 0    | 0   | 24  | 1   | 0  | 0   | 3    | 1   | 0.   | ÷.   | 1    | 1    |

#### D. Power Factor

Power factor is the ratio between real power and apparent power in a circuit. The formula for power factor is

$$Power \ factor = \frac{Active \ Power}{Apparent \ Power} = \frac{P}{s}$$

(1)

where  $\theta$  is the angle difference (in degrees) between output voltage and output current. Unity power factor is the best. The load with higher power factor will draw less currents, hence decrease the lost in distribution system and therefore wasted energy will be less.

#### E. Total Harmonic Distortion (THD)

THD is a measurement of the harmonic distortion is defined as the ratio of the sum of the powers of all harmonic components to the power of the fundamental frequency. It can be presented by expression below

$$THD = \frac{\sqrt{I_2^2 + I_3^2 + I_4^2 + \dots + I_{60}^2}}{I_1} \tag{2}$$

Formula above is for the current waveform. THD is used to characterize the linearity of a systems and the power quality of electric power systems.

According to IEEE standard of THD limits, total harmonic current distortion shall be less than 5% of the fundamental frequency current at rated inverter output [9]. The THD for simulated model will be shown in Section IV.

F. Efficiency

In general, efficiency is a measurable concept, quantitatively determined by the ratio of output to input. In this system, input power is the power delivered from PV arrays, while the output power is the power at the grid. PV array's voltage must be higher than of *Vgrid* to inject current into the grid, or current will be injected from the grid into the inverter. This means that PV arrays must be the one that deliver the power for the grid, so that the grid can consume the power.

## **III. MODULATION TECHNIQUE**

A. PWM Modulation Technique for 5-level Multilevel Inverter

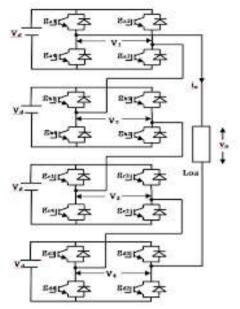

The modulation technique used in this inverter topology is sinusoidal pulse width modulation (SPWM) technique. The principle is to generate gate signal by comparing a triangular carrier signal with two reference (sinusoidal) signals, which having same frequency and in phase, but different offset voltages as shown in Figure 4.

Figure 4. PWM switching signal generation for 5-level multilevel inverter.

According to the amplitude of the voltage reference, V*ref*, the operational interval of each mode varies within a certain period. The modes are separated as

Mode 1:  $0 \le \acute{\omega}t \le \theta_1 \& \theta_2 \le \acute{\omega}t \le \prod$ Mode 2:  $\theta_1 < \acute{\omega}t \le \theta_2$ Mode 3:  $\prod < \acute{\omega}t \le \theta_3 \& \theta_4 \le \acute{\omega}t \le 2 \prod$ Mode 4:  $\theta_3 \le \acute{\omega}t \le \theta_4$

The phase depends on the modulation index. The modulation index of the proposed five-level PWM inverter is defined as :

$$M = \frac{Am}{2Ac} \quad (3)$$

where AM is the peak value of reference voltage and AC is the peak value of carrier wave. The modulation index recommended in this technique is to be between 0.66 and 1.

#### B. PWM Modulation Technique for 7-level Multilevel Inverter

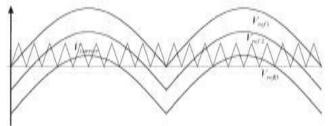

Seven level multilevel inverter's PWM modulation contain three reference signal named Vref1, Vref2, and Vref3. These three reference signals had same frequency, amplitude and phase. The difference is that they had different offset values. The reference signals are positive sine waveform. To produce the signals for the switches, the reference signals need to be compared to a carrier signal (Vcarrier); a triangular wave signal, using a comparator.

The reference signals were each compared with the carrier signal. If Vref1 had exceeded the peak amplitude of Vcarrier, Vref2 was then compared with Vcarrier until it had exceeded the peak amplitude of Vcarrier. Then, Vref3 would be compared with Vcarrier until it reached zero. Once Vref3 had reached zero, Vref2 would be compared until it reached zero. Then, onward, Vref1 would be compared with V carrier [8] and the process continues. Figure 4 shows the signal generation.

Figure 4. PWM switching signal generation for 7-level multilevel inverter.

Six modes were operated in one cycle of this inverter and described as follows

The phase angle depends on modulation index. For dual reference signal used in 7-level modulation technique, equation (1) was used. Therefore, for three reference signals, the modulation index is defines as

$$M = \frac{Am}{2Ac} \tag{4}$$

C.PWM Modulation Technique for 9-level Multilevel Inverter.

Nine level multilevel inverter's PWM modulation contain three reference signal named Vref1, Vref2, and Vref3. These three reference signals had same frequency, amplitude and phase. The difference is that they had different offset values. The reference signals are positive sine waveform. To produce the signals for the switches, the reference signals need to be compared to a carrier signal (Vcarrier); a triangular wave signal, using a comparator.

The reference signals were each compared with the carrier signal. If Vref1 had exceeded the peak amplitude of Vcarrier, Vref2 was then compared with Vcarrier until it had exceeded the peak amplitude of Vcarrier. Then, Vref3 would be compared with Vcarrier until it reached zero. Once Vref3 had reached zero, Vref2 would be compared until it reached zero. Then, onward, Vref1 would be compared with V carrier [8] and the process continues. Figure 5 shows the signal generation.

Figure 5. PWM switching signal generation for 9-level multilevel inverter.

Eight modes were operated in one cycle of this inverter and described as follows

$\begin{array}{ll} \text{Mode 7:} & \theta_5 < \acute{\omega} t \leq \theta_6 \& \theta_7 < \acute{\omega} t \leq \theta_{10} \\ \text{Mode 8:} & \theta_8 < \acute{\omega} t < \theta_{10} \end{array}$

IV. RESULTS AND DISCUSSIONS TABLE IV. SIMULATION'S RESULT SUMMARY

| Factor     | 5-level    | 7-level    | 9-level    |

|------------|------------|------------|------------|

| Output     | Sinusoidal | Sinusoidal | Sinusoidal |

| Current    |            |            |            |

| Filter     | L: 7mH x   | L: 5mH x   | L: 3mH x   |

|            | 2          | 2          | 2          |

|            | C: 2200    | C: 2200    | C: 2200    |

|            | uF         | uF         | uF         |

| Power      | 0.861      | 0.913      | 0.965      |

| factor     | (lagging)  | (lagging)  | (lagging)  |

| THD        | 1.876%     | 1.175%     | 0.474%     |

| Efficiency | 67.9%      | 88.5%      | 94.29%     |

From Table IV, it shows that the values of filters used in 9level multilevel inverter are smaller than filters used in 7-level and 5-level multilevel inverter. The smaller the filter size, the less cost needed to implement the model.

The power factor also shows that 9-level multilevel inverter is closer to unity power factor than 7-level and 5-level multilevel inverter. As widely known, unity power factor is ideal because it means that no energy wasted in the system. In reality, closing the value of power factor to 1 is as far as it can be and power factor value of 9-level multilevel inverter is better than the value for 5-level and 7-level multilevel inverter.

For the THD value, all 3 levels had given the results that satisfy the IEEE standard of THD limit as mentioned in Section II, which is below 5%. Therefore, all 3 levels have acceptable value of THD, despite 9-level multilevel inverter having smaller THD compared to 7-level & 5-level multilevel inverter.

For the efficiency, it is obvious that 9-level multilevel inverter gave better efficiency value than 5-level as well as 7level and that means 9-level multilevel inverter is more efficient than the other two.

## CONCLUSION

The use of multilevel inverter in power system was accepted in power system since it gave a lot of advantages. More number of levels of multilevel inverter will give better performance in the system. In this paper, from the results, 9level multilevel inverter had given more efficient performance in terms of the power factor, THD and its efficiency than 7level & 5-level multilevel inverter. It also is more suitable for the purpose of integrating PV arrays and grid system.

#### References

- S.J. Park, F.S. Kang, M.H. Lee, C.U. Kim, "A New Single-Phase Five-Level PWM Inverter Employing a Deadbeat Control Scheme", IEEE Transactions on Power electronic, Vol. 18, No. 3, May 2003, pp. 831-843

- [2] A. K. Panda, Y. Suresh, "Research on Cascade Multilevel Inverter with Single DC Source by using Three-phase Transformers", Electrical Power and Energy System, Vol 40, March 2012, pp. 9-20.

- [3] B. Singh, N. Mittal, K. S. Verma, "Multi-Level Inverter: A Literature Survey On Topologies And Control Strategies", International Journal of Reviews in Computing, Vol. 10, July 2012, pp. 1-16.

- [4] N.A. Rahim, K. Chaniago, J. Selvaraj, "Single-Phase Seven-Level Grid Connected Inverter for Photovoltaic System", IEEE

Transactions on Industrial Electronics, Vol. 58, No. 6, June 2011, pp. 2435-2443.

- [5] V.G. Agelidis, D.M. Baker, W.B. Lawrance, C. V. Nayar, "A Multilevel Inverter Topology for Photovoltaic Applications", in IEEE International Sysmposium on Industrial Electronics, ISIE '97, Vol. 2, July 1997, pp.

- [6] P. Satheesh Kumar, Dr S. P. Natrajan, Dr. Alamelu Nachiappan, Dr. B. Shanthi, "Performance Evaluation of Nine Level Modified CHB Multilevel Inverter for Various PWM Strategies," IJMER, Vol. 3.Issue. 5, Sept-Oct. 2013 pp-2758-2766.

- [7] N.A. Rahim, J. Selvaraj, "Multilevel Inverter for Grid Connected PV System Employing Digital PI Controller", IEEE Transactions on Industrial Electronics, Vol. 56, No. 1, Jan 2009, pp. 149-158.

- [8] N.A. Rahim, J. Selvaraj, "Multilevel Inverter for Grid Connected PV System Employing Digital PI Controller", IEEE Transactions on Industrial Electronics, Vol. 56, No. 1, Jan 2009, pp. 149-158.

- [9] Ranganathan Gurunathan and Ashoka K. S. Bhat."A Zero-Voltage Transition Boost Converter Usingva Zero-Voltage Switching Auxiliary Circuit". PowervElectronics, IEEE Transactions on Volume 17,vIssue 5, Sept. 2002 Page(s):658 – 668.