# Common Mode Voltage reduction in Diode Clamped MLI using Alternative Phase Opposition Disposition SPWM Technique

<sup>1</sup>Mohd Esa, <sup>2</sup>J.E.Muralidhar <sup>1</sup>M.E. Student, <sup>2</sup>Associate Professor <sup>1,2</sup>Electrical Engineering Department <sup>1, 2</sup> Muffakham Jah College of Engineering and Technology, Hyderabad, India

*Abstract:* The main objective of this paper is to reduce the Common Mode Voltage (CMV) in the Diode Clamped Multilevel Inverter (DCMLI). Three phase Y-connected RL load is connected to DCMLI. The common mode voltage exists between neutral point of Y-connected load and system ground. CMV causes premature failure of bearings of induction motor and is essential to reduce. In this paper, Alternative Phase Opposition Disposition SPWM technique is used to reduce common mode voltage. Two level, five level, seven level and nine level DCMLI are compared in terms of THD and CMV. The effect of a passive LC filter on THD was studied. The simulation of circuit is carried out by using MATLAB/Simulink. Simulation result portrays reduction in THD and CMV by using APOD-SPWM controlled higher level Inverters.

#### IndexTerms - CMV, THD, APOD SPWM, DCMLI

#### I. INTRODUCTION

CMV is define as voltage between neutral point of the load and the dc midpoint or the voltage between neutral point of load and the system ground or the common mode voltage is defined as the potential of the star point of the load with respect to the center of the D.C. bus of the inverter (or) the common mode voltage (CMV) of the 3-phase system is defined as the voltage potential difference between the star point of the load network and the mid-point of the D.C. link capacitors[1].

$$CMV = \frac{1}{3} \sum_{x=a}^{c} V_{xg}$$

(1)

Where  $V_{ag}$ ,  $V_{bg}$ ,  $V_{cg}$  are the voltages between ground to phase.CMV is zero in purely sinusoidal three phase system but VSI is nonpure sinusoidal system thus it develops CMV. CMV results in high leakage current and premature failure of motor bearing so it is required to reduce [2], [3]. Some modulation techniques based approaches to reduce CMV are MLI using SPWM technique, MLI using Space Vector PWM technique, MLI using Modified space vector modulation technique, predictive current control method, on zero state modulation techniques. In this paper, APOD- SPWM is used to reduce common mode voltage.

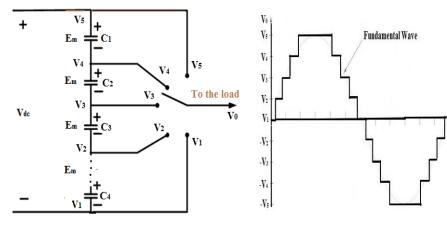

Fig.1.Schematic of single pole of MLI by a switch [5]

The idea of multilevel inverters has been introduced in 1975 with invention of cascaded H-Bridge MLI. The term multilevel began with 3- level inverter. Afterwards numerous multilevel inverter topologies have been developed. Three different MLI topologies that have been proposed are diode clamped or neutral point clamped, flying capacitor and cascaded H-Bridge or multicell MLI [4]. In addition, several control strategies have been developed. The series connected capacitors constitute the energy tank for the inverter, providing some nodes to which MLI can be connected. Each capacitor has the same voltage  $E_m$ , which is given by

$$E_{\rm m} = \frac{E_{\rm dc}}{{\rm m}-1} \tag{2}$$

Where m denotes the number of levels. The term level refers to number of nodes to which the inverter can be accessible. An m-level inverter needs m-1 capacitors. Figure 2 shows the schematic of a pole in MLI.Pole is regarded as a single-pole, multi-throw switch. Desired output can be obtained by connecting the switch to one node at a time.

Different modulation techniques exist to trigger switches of inverter circuit. The commonly used modulation techniques are as follows

- Sinusoidal pulse width modulation (SPWM) [6]

- Third harmonic PWM (THPWM)

- Space vector PWM (SVPWM) [7]

- Modified Space vector PWM (MSVPWM)

The most popular method of controlling inverter's output voltage is SPWM technique.SPWM is a carrier based pulse width modulation method in which predefined modulation signal is used to determine output voltages. Sinusoidal modulation signal is used in SPWM technique. The gating signal in SPWM is generated by comparing a reference signal of sine shape with a triangular carrier wave.

Fig.3.Comparision of reference and carrier signal in SPWM generation

The width of each pulse varied proportionally to amplitude of a sine wave. The output frequency of a inverter can be found by using the frequency of reference signal. The rms output voltage can be controlled by modulation index and intern modulation index is controlled by peak amplitude.SPWM method results in reduction of THD for output voltage.SPWM technique is effective modulation technique and it does not require any additional components and eliminates lower order harmonics easily. Carrier based SPWM techniques are classified as follows

- Single carrier based SPWM technique

- Multi carrier based SPWM technique

Single carrier SPWM technique is used for 2-level inverter whereas multi carrier SPWM technique is used in Multi-level inverters. Multi carrier SPWM technique is further classified as follows

- Phase shift SPWM technique

- Level shifted SPWM technique

- Hybrid SPWM technique

Level shifted SPWM technique is further classified as follows

- Phase Disposition (PD)

- Phase Opposition Disposition (POD)

- Alterative Phase Opposition Disposition (APOD)

Alternative phase opposition disposition SPWM is used to reduce common mode voltage in Diode clamped MLI.

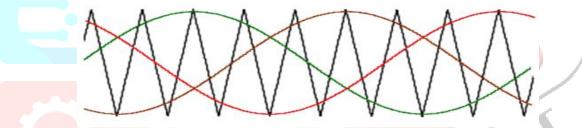

### II. DIODE CLAMPED MULTILEVEL INVERTER

Diode clamped Inverter (DC-MLI) is also known as neutral point clamped inverter (NPC-MLI). A m level diode clamped inverter typically consists of (m-1) capacitors on the D.C. bus and produces m levels on the phase voltage. The m- level inverter leg requires (m-1) capacitors,  $2 \times (m-1)$  switching devices and  $(m-1) \times (m-2)$  clamping diodes [8].

For one phase, steps to synthesize the five level voltages are as follows.

- 1. Turn on all upper half switches of Limb-A i.e., from SW1 to SW4 for an output voltage level  $V_{a0} = V_{dc}/2$ .

- 2. Turn on three upper switches of Limb-A i.e., SW2 to SW4 and one lower switch of Limb-A i.e., SW5 for an output voltage level  $V_{a0} = V_{dc}/4$ .

- 3. For an output voltage level  $V_{a0} = 0$ , turn on two upper switches SW3 and SW4 of Limb-A and two lower switches SW5 and SW6 of Limb-A.

- 4. Turn on one upper switch SW4 of Limb-A and three lower switches SW5 to SW7 of Limb-A for an output voltage level  $V_{a0} = -V_{dc}/4$ .

- 5. Turn on all lower half switches from SW5 to SW8 of Limb-A for an output voltage level  $V_{a0} = -V_{dc}/2$

| Table 1: Switching states of | of five level diode clam | ped inverter for phase A |

|------------------------------|--------------------------|--------------------------|

|                              |                          |                          |

| Switching States |      |      |            |      |      | Output      |             |         |

|------------------|------|------|------------|------|------|-------------|-------------|---------|

| SW1              | SW2  | SW3  | <i>SW4</i> | SW5  | SW6  | <i>SW</i> 7 | <i>SW</i> 8 | voltage |

| High             | High | High | High       | Low  | Low  | Low         | Low         | Vdc/2   |

| Low              | High | High | High       | High | Low  | Low         | Low         | Vdc/4   |

| Low              | Low  | High | High       | High | High | Low         | Low         | 0       |

| Low              | Low  | Low  | High       | High | High | High        | Low         | -Vdc/4  |

| Low              | Low  | Low  | Low        | High | High | High        | High        | -Vdc/2  |

Seven level and nine level diode clamped inverters can also be presented in same manner as five level DCMLI

## **III. ALTERNATIVE PHASE OPPOSITION DISPOSITION SPWM STRATEGY**

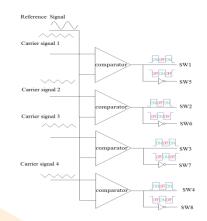

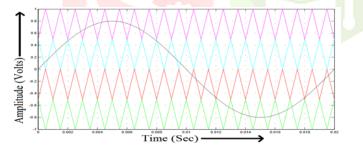

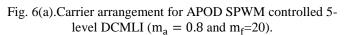

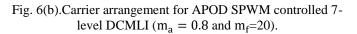

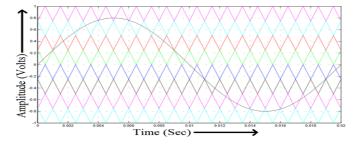

In APOD-SPWM technique the carrier signal of same amplitude are phase displaced from each other by  $180^{\circ}$  from its neighboring carrier signals, This carriers are compared with sinusoidal signal for producing pulse signals to trigger gates of switches used in DCMLI.For m-level output, (m-1) carrier signals are phase disposed by 180 degrees to its neighboring carrier waveform [9]. Fig. 6(a), 6(b), and 6(c) shows the carrier arrangement for APOD SPWM controlled 5, 7 and 9 level DCMLI respectively

Fig. 5. APOD-SPWM technique for triggering switches of five level diode clamped inverter (Phase A)

The amplitude modulation index  $m_a$  and frequency ratio  $m_f$  are mathematically shown in equations (3) and (4) respectively.

$$m_{a} = \frac{A_{m}}{(m-1)A_{cr}}$$

(3)

Where  $A_m$  is peak to peak amplitude of reference waveform or modulating signal,  $A_{cr}$  is peak to peak amplitude of individual carrier frequency, m is output level of inverter.

Amplitude (Volts)

$$m_f = \frac{f_{cr}}{f_m}$$

Where  $f_{cr}$  is frequency of carrier signal &  $f_m$  is frequency of modulating signal.

Time (Sec)

Fig. 6(c).Carrier arrangement for APOD SPWM controlled 9-level DCMLI ( $m_a = 0.8$  and  $m_f=20$ ).

(4)

# **IV. SIMULATION RESULTS**

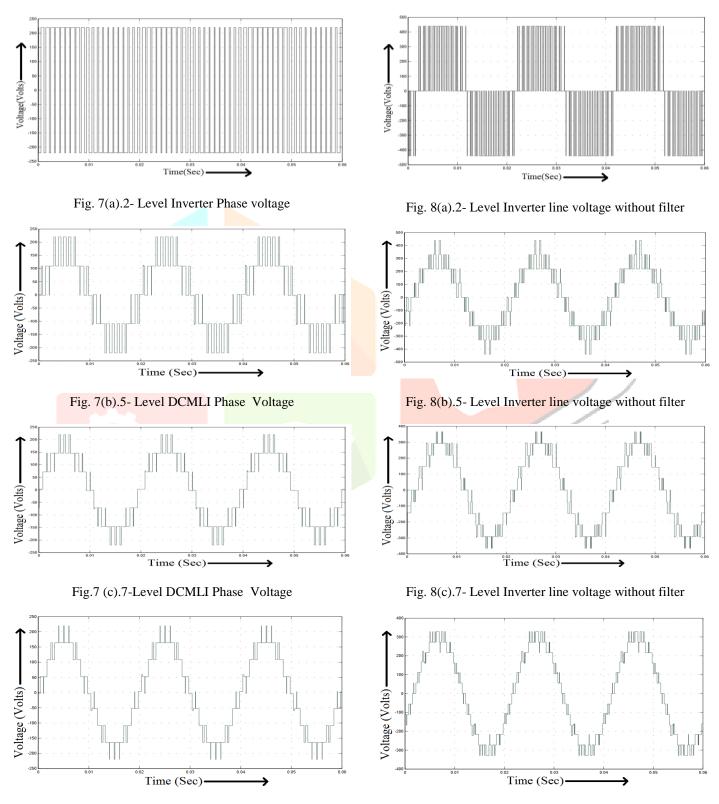

The Simulation of APOD-SPWM controlled DCMLI for five, seven and nine level is carried out in Matlab/Simulink software. Figures 7(a), 7(b), 7(c), 7(d) presents phase voltage for 2-level, 5-level, 7-level, 9-level inverter respectively and figures 8(a), 8(b), 8(c), 8(d) presents line voltage without filter for 2-level, 5-level, 7-level, 9-level inverter respectively.

Fig. 7(d).9- Level DCMLI Phase Voltage

Fig. 8(d).9- Level Inverter line voltage without filter

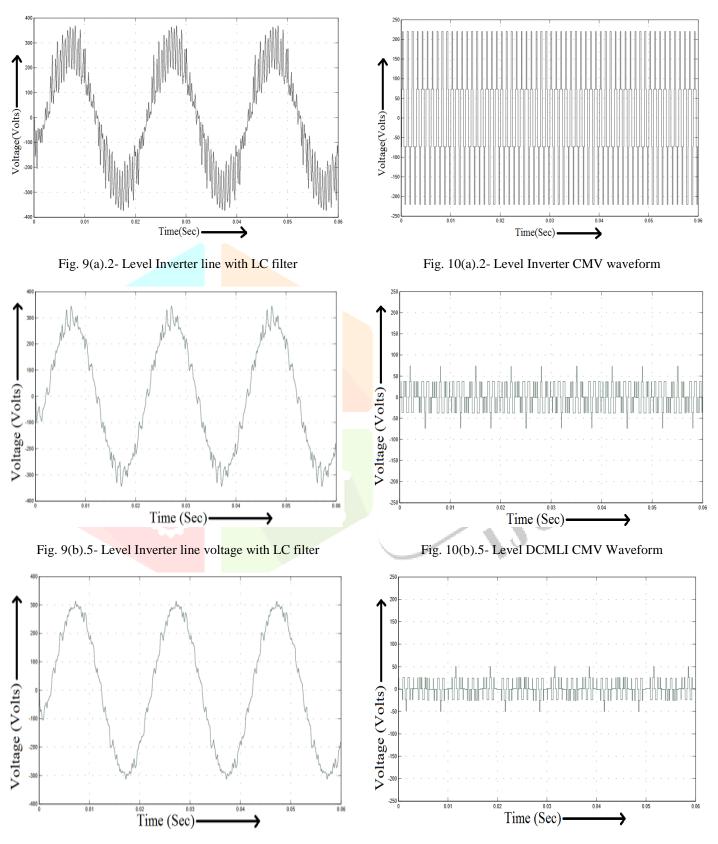

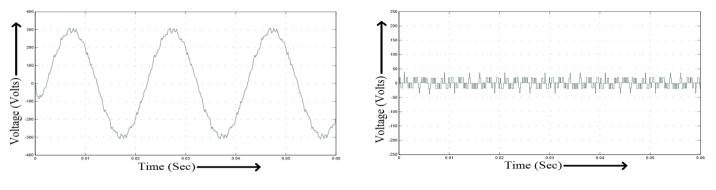

Figures 9(a), 9(b), 9(c), 9(d) presents line voltage with filter for 2-level, 5-level, 7-level, 9-level inverter respectively and figure 10(a), 10(b), 10(c), 10(d) presents CMV waveform for 2-level, 5-level, 7-level, 9-level inverter respectively.

Fig. 9(c).7- Level Inverter line voltage with LC filter

Fig. 10(c).7-Level DCMLI CMV Waveform

584

Fig. 9(d).9- Level Inverter line voltage with LC filter

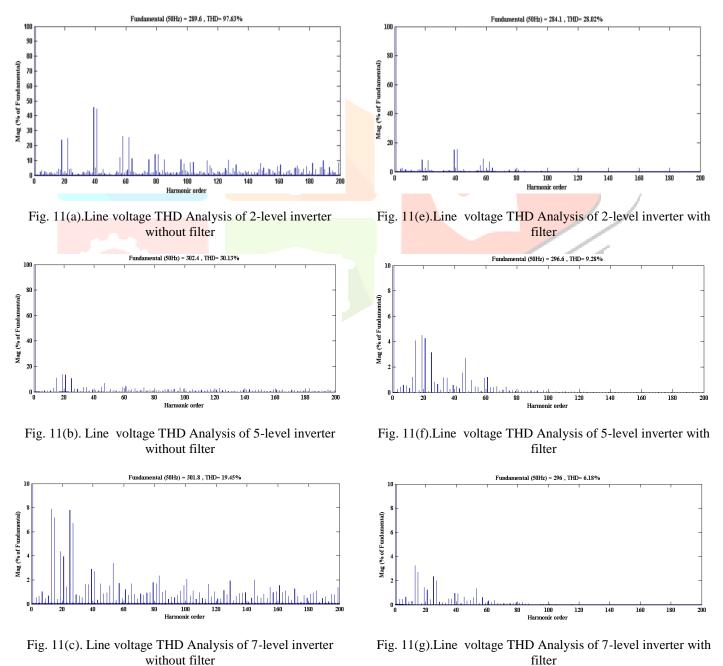

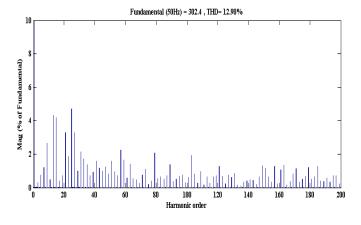

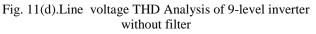

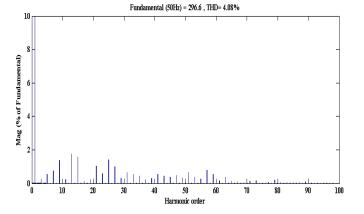

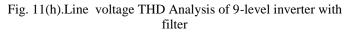

Figure 11(a), 11(b), 11(c), 11(d) presents THD analysis without filter for 2-level, 5-level, 7-level, 9-level inverter respectively and figure 11(e), 11(f), 11(g), 11(h) presents THD analysis with LC filter for 2-level, 5-level, 7-level, 9-level inverter respectively.

IJCRT1812942 International Journal of Creative Research Thoughts (IJCRT) www.ijcrt.org

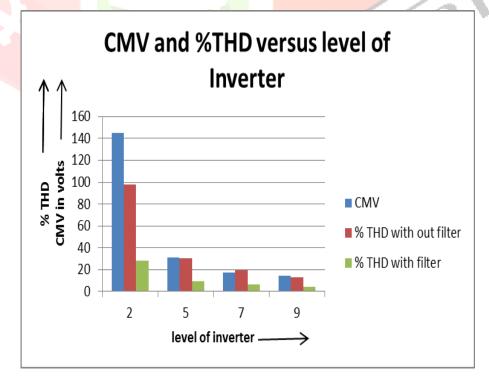

Table 2 shows the CMV and %THD for two level VSI, 5, 7 and 9 level Diode clamped Inverter using Alternative Phase Opposition Disposition SPWM technique with and without LC filter.

|     |                                               | 2-level | 2-level 3-Phase APOD SPWM Controlled DCM |         |         |  |

|-----|-----------------------------------------------|---------|------------------------------------------|---------|---------|--|

|     |                                               | VSI     | 5-level                                  | 7-level | 9-level |  |

| C   | CMV<br>(V)                                    | 145.2   | 31.14                                    | 17.44   | 14.09   |  |

| THD | Wi <mark>thout</mark><br>fil <mark>ter</mark> | 97.63   | 30.13                                    | 19.45   | 12.90   |  |

| (%) | With filter                                   | 28.02   | 9.28                                     | 6.18    | 4.08    |  |

Variation of CMV and % THD with level of Inverter is shown in fig. 12

### V.CONCLUSION

APOD SPWM controlled DCMLI for five, seven & nine level is simulated in Matlab/Simulink software. It is cleared from fig. 12 that CMV and %THD decreases with increase in level of the inverter. Increase in level improves the nature of output voltage waveform, approaching to sine shape which in turn lessens lower order harmonics. The number of steps in the output voltage increases as the level increases which reduces rate of rise of voltage.CMV and %THD reduces as size of step reduces.

#### REFERENCES

- E. Un and A. M. Hava, "A Near State PWM Method with Reduced Switching Losses and Reduced Common Mode Voltage for 3-Phase Voltage Source Inverters," Industry Applications, I.E.E.E. transactions on, vol. 45, pp. 782-793, 2009

- [2] Min Zhang, "Investigation of Switching Schemes for 3-phase Four Leg Voltage Source Inverters", A thesis submitted for the degree of Doctor of Philosophy June, 2013, School of Electrical and Electronic Engineering, Newcastle University

- [3] Anuradha V.Jadhav and Mrs.P.V.Kapoor, "Reduction of Common Mode Voltage using Multilevel Inverter", Energy Efficient Technologies for Sustainability [ICEETS],pp.586-590,06 October 2016,DOI: 10.1109/ICEETS.2016.7583822,I.E.E.E.

- [4] T. Cunnyngham. Cascade Multilevel Inverters for Hybrid-Electric Vehicle Applications with Variant DC Sources. Master's thesis, The University of Tennessee, 2001.

- [5] Muhammad H. Rashid,"Power Electronics-Circuits, Devices and Applications" Pearson Education Incorporated, 2005.

- [6] P. G. Shewane, S. Gaigowal, B. Rane, "Multicarrier Based SPWM Modulation for Diode Clamped MLI to reduce CMV and THD", Power, Automation and Communication [INPAC-2014], International Conference at Amravati on 6-8 OCT.2014, pp. 50-54, DOI:10.1109/INPAC.2014.6981134, IEEE.

- [7] Sk. Moin Ahmed, Haitham Abu-Rub, Zainal Salam, "Common Mode Voltage Elimination in a Three-to-Five-Phase Dual Matrix Converter Feeding a Five-Phase Open-End Drive Using Space-Vector Modulation Technique", IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 62, NO. 10, OCTOBER 2015.

- [8] A.Nabae, I. Takahashi, H.Akagi'A new Neutral Point Clamped PWM Inverter'' I.E.E.E. transactions on Industry applications, Vol. IA-I7, No.5, pp.518-52 September/October, 1981.

- [9] McGrath, B.P.; Holmes, D.G.; "Multicarrier PWM strategies for Multilevel Inverters," Industrial Electronics, I.E.E.E. transactions, vol.49, no.4, pp. 858-867, August 2002, DOI:10.1109/TIE.2002.801073

587