# SIMULATION AND ANALYSIS OF DPFC FOR VOLTAGE SAG AND SWELL MITIGATION

Pushpak Patel<sup>1</sup>, Maharshi Mehta<sup>2</sup>, Ashish Patel<sup>3</sup>

1,3</sup>Assistant Professor, Electrical Department, LDRP-ITR, Gandhinagar, Gujarat, India

<sup>2</sup>PG Scholar, Electrical Department, LDRP-ITR, Gandhinagar, Gujarat, India

Abstract: Now a day's power system facing a power quality problem due to increase in power demand and increase in industrial plants. Good power quality means the power supply which can always available within voltage and frequency tolerance and also these are harmonic free and pure sinusoidal shape. This paper describes the power flow control in transmission line with Flexible AC Transmission System (FACTS) family, called Distributed Power Flow Controller (DPFC). The DPFC is derived from the Unified Power Flow Controller (UPFC). The DPFC can be considered as UPFC with an eliminated common DC link, to enable the independent operation of the shunt and the series converters which enhances the effective placement of the series and shunt converters. The active power exchange between the two converters, which is through the common dc link in the UPFC, is now through the transmission lines at the third-harmonic frequency in the DPFC. DPFC is used to mitigate the voltage sag and swell as a power quality issue. The DPFC have the same control capability as the UPFC, which comprises the adjustment of the line impedance, the transmission angle, and the bus voltage. In DPFC three-phase series converter is divided to several single-phase series distributed converters through the transmission line.

#### INTRODUCTION

A Power Quality problem can be defined as deviation of magnitude and frequency from the ideal sinusoidal waveform. Good power quality is benefit to the operation of electrical equipment, but poor power quality will produce great harm to the power system. Most of the electronic equipments such as personal computers, telecommunication equipments, microprocessor and micro controller, etc are responsible for power quality problems. A Power Quality problem can be defined as deviation of magnitude and frequency from the ideal sinusoidal wave from. Good power quality is benefit to the operation of electrical equipment, but poor power quality will produce great harm to the power system [1]. Harmonics are defined as sinusoidal wave form having a frequency equal to an integer multiple of the power system fundamental frequency. It is a component of a periodic waveform. If the fundamental frequency multiple is not an integer, then we are dealing with inter harmonics [1]. Most of the electronic equipments such as telecommunication computers, equipment, microprocessors, and microcontrollers etc; are generally responsible to Power Quality problems. A poor power quality has become a more important issue for both power suppliers and customers. Poor power quality means there is a deviation in the power supply to cause equipment malfunction or may failure. To solve the power quality problem the power electronic devices such as flexible alternating-current transmission system (FACTS) and custom power devices (DVR) which are used in transmission and distribution control, respectively, should be developed. The impact of transient parameters in majority of transmission lines problems such as sag (voltage dip), swell (over voltage) and interruption, are also considerable [5]. To mitigate the mentioned power quality problems, the utilization of FACTS devices such as power flow controller (UPFC) and synchronous static compensator (STAT-COM) can be helpful. The distributed power flow controller (DPFC) is presented which has a similar configuration to UPFC structure.

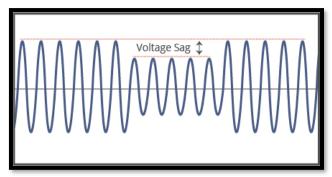

#### **VOLTAGE SAG**

Voltage sags and momentary power interruptions are probably the most important Power Quality problem affecting industrial and large commercial customers. These events are usually associated with a fault at some location in the supplying power system. Interruptions occur when the fault is on the circuit supplying the customer. But voltage sags occur even if the faults happen to be far away from the customer's site. Voltage sags lasting only 4-5 cycles can cause a wide range of sensitive customer equipment to drop out. To industrial customers, voltage sag and a momentary interruption are equivalent if both shut their process down. A typical example of voltage sag is shown in fig.1

Fig.1- Voltage Sag condition

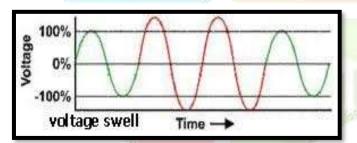

# VOLTAGE SWELL

A swell is the reverse form of Sag, having an increase in AC Voltage for duration of 0.5 cycles to 1 minute's time. For swells, high-impedance neutral connections, sudden large load reductions, and a single-phase fault on a three phase system are common sources. Swells can cause data errors, light flickering, electrical contact degradation, and semiconductor damage in electronics causing hard server failures. Our power conditioners and UPS Solutions are common solutions for swells. It is important to note that, much like sags, swells may not be apparent until results are seen. Having your power quality devices monitoring and logging your incoming power will help measure these events.

Fig.2-Voltage swell condition

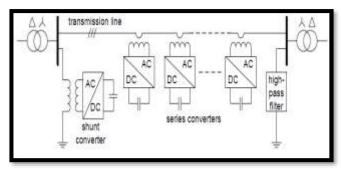

#### **DPFC Working**

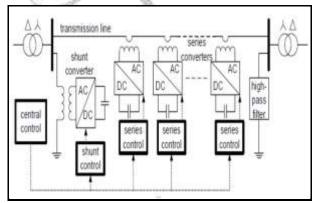

The DPFC is composed of a single shunt converter and multiple independent series converters as shown in Figure 3, which is used to balance the line parameters, such as line impedance, transmission angle and bus voltage magnitude. To detect the voltage sags and determine the three single phase reference voltages of DPFC, the SRF method is also proposed as a detection and determination method.

Fig 3: DPFC configuration

To reduce the failure rate of the components by selecting components with higher ratings than necessary or employing redundancy at the component or system levels are also options. Unfortunately, these solutions increase the initial investment necessary, negating any cost-related advantages. Accordingly, new approaches are needed in order to increase reliability and reduce cost of the UPFC and DPFC at the same time. The elimination of the common DC link also allows the DSSC concept to be applied to series converters. In that case, the

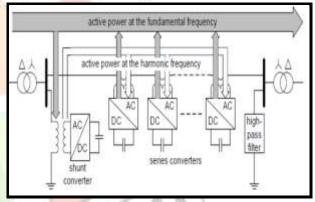

Fig.4 Active power exchange in dpfc

Fig.5 DPFC Control

reliability of the new device is further improved due to the redundancy provided by the distributed series converters. Unlike in UPFC where the active power transfer is through the DC link between the series and shunt converters here in DPFC this power flow is through the transmission lines at the third

harmonic frequency which is a zero-sequence component and can be naturally blocked by a Y-Δ transformer. The DPFC makes use of the distributed FACTS (D-FACTS) in the design of the series converter, which is to use multiple single-phase converters instead of one large rated three phase converter while the shunt converter remains as static synchronous compensator (STATCOM) as in UPFC. These large numbers of series converters provides redundancy, thereby increasing the system reliability. As the D-FACTS converters are single phase and floating with respect to the ground, there is no high voltage isolation required between the phases. Accordingly, the cost of the DPFC system is lower than the UPFC. The controllability of the DPFC is same as that of the UPFC which refers to the adjustment of the line impedance, the transmission angle, and the bus voltage. The operation principle, the modelling and control, and experimental demonstrations of the DPFC are presented in this paper.

# Simulation & Results

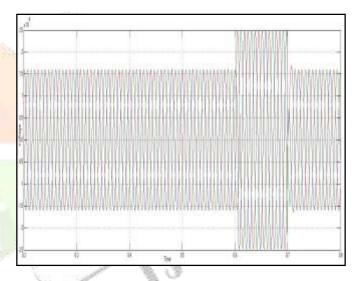

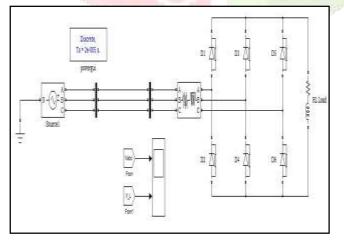

Fig-6 Voltage Sag condition in 3-phase system

There is 3-phase fault is created in the three phase system which creates voltage sag problem in this system. The three phase fault is operated and controlled through external timer signal. The Simulation of this model shows that voltage Sag condition occurs at input side and the point of common coupling.

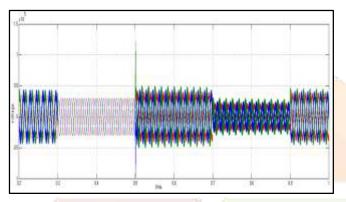

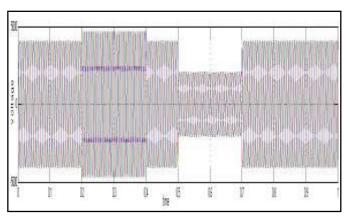

Fig.7 Waveform of Voltage Sag at PCC (Point of Common Coupling) point

Above figure shows that voltage sag is occurs in the interval of 0.3 to 0.5.

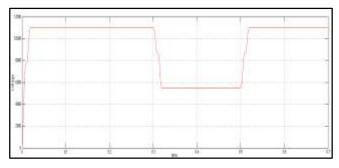

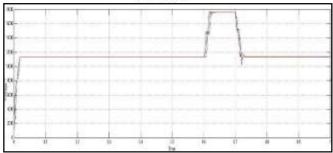

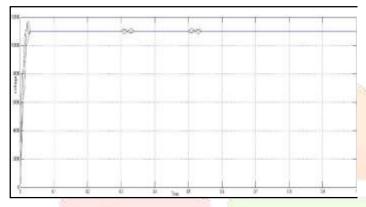

Fig 8 R.M.S value during Voltage Sag condition at point of common coupling

Above figure shows that voltage magnitude is reduced to below 6kv during voltage sag condition

### MATLAB simulation of voltage sag mitigation

# using DPFC

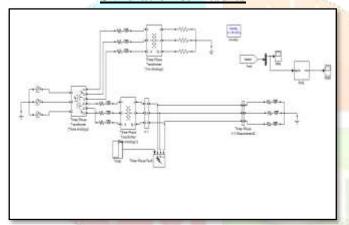

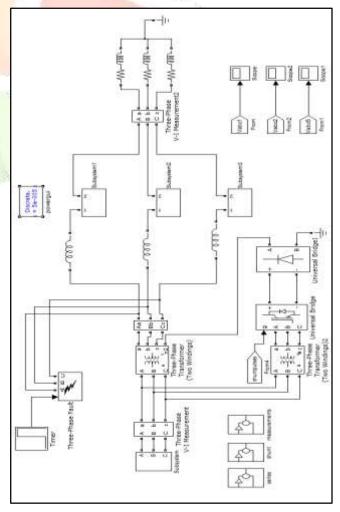

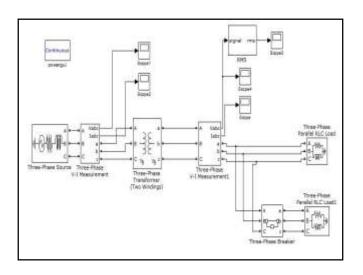

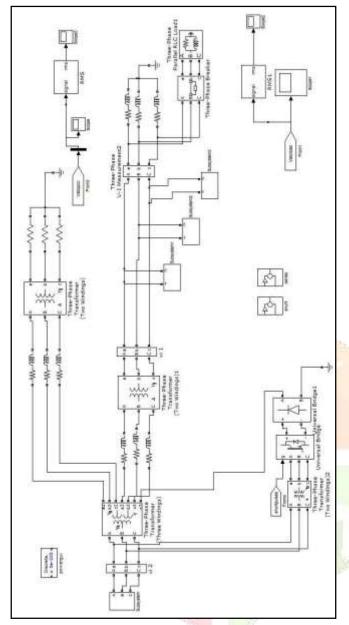

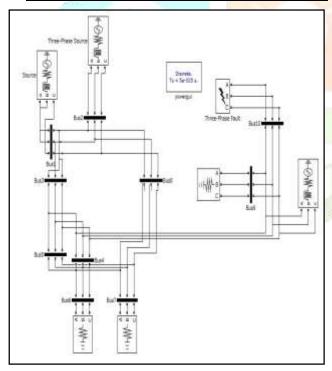

Fig.9 Simulation of Voltage sag mitigation using DPFC.

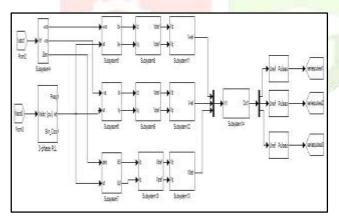

In the above fig.9 its show the voltage sag mitigation using DPFC. There two converters are used in the circuit. 1) Shunt converter 2) series converter. Shunt converter is used to mitigate the currents related problem and series converter is used to mitigate the voltage related problem. Shunt converter is connected to the grid and series converter is connected in individual phases. In source subsystem we are using timer based voltage source and in series subsystem we are using the capacitor and it working with his charging and discharging principle. V-I measurement is connected to measure the source side voltage. From the source side shunt converter is connected. Three phase is connected to delta- star transformer converter is used to converter the AC to DC. PWM is connected to the converter to control or give appropriate widths which require mitigating the current related problem. So to maintain the continue power shunt converter is connected to the grid. 3phase fault is created at PCC to develop the voltage sag condition. After creating the voltage sag condition is each phase series converter will operate to mitigate the voltage sag condition. In series sub system two mainly block are used 1) sequence analyzer with PI control 2) phase lock loop block. Sequence analyzer is used to maintain the positive sequence, negative sequence and zero sequence of current. PLL block is use for the angular frequency. Then 3 phase quantity is convert into the d-q quantity. After generating id, iq and vd, vq its will convert into the 3 phase (a,b,c). Again PWM is generating the pulses to mitigate the voltage sag problem.

Fig 10 Series Converter Subsystem

Fig.11 Shunt Converter Subsystem

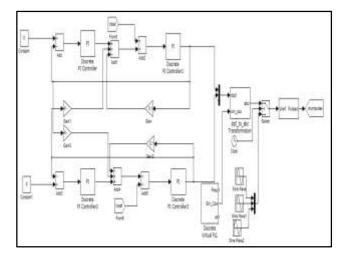

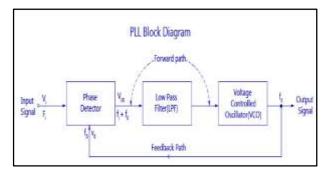

#### PLL LOOP CONTROL (Phase Locked Loop control)

Here phase detector will compare input frequency and feedback frequency and after that it will generate Ver (error voltage) which is DC voltage that DC voltage goes in to low pass filter so LPF removes high frequency noise and produces steady DC level.

That steady DC voltage level pass through voltage controlled oscillator (vco) and so that output frequency directly proportional to input signal and it try to do equal input and output frequency.

### PI CONTROL (Proportional Integral Control)

A PI controller which continuously calculates an error value as the difference between a desired set point (sp) and a measured process variable (pv) and applies a correction based on proportional and integral terms. The PI controller is the sum of the instantaneous error values over the time and gives the accumulated offset that should have been corrected previously. The controller (an analogue/digital circuit, and software), is trying to keep the controlled variable such as temperature, liquid level, motor velocity, robot joint angle, at a certain value called the set point (sp).

A feedback control system does this by looking at the error (E) signal, which is the difference between where the controlled variable (called the process variable (PV)) is, and where it should be. Based upon the error signal, the controller decides the magnitude and the direction of the signal to the output.

Proportional (P) accounts for the present values of the (sp-pv), if the error is the large and positive. Then proportional control alone will always have an error between the set point and the actual process value because it requires the error to generate the proportional response if there is no error no response. Integral control (I) accounts for the past values of (sp-pv) and integrates

them over the time to produce the I term and it will add the error value (sp-pv) until it gets the proper output.

Fig.12 PLL loop control

# **Voltage waveform after using DPFC**

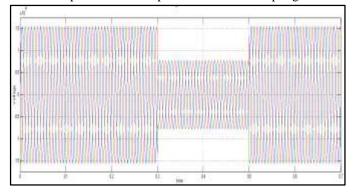

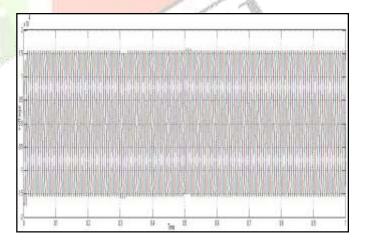

Fig 13 Waveform of voltage sag due to fault and source dip in time 0.2 to 1 sec.

Fig 14 Waveform of voltage sag at source side in time 0.5 to 1 sec.

Fig.15 converter injecting voltage in voltage dip

Fig.16 converter injecting voltage in fault sag

Fig.17 constant output voltage after using DPFC in time o.5 to 1 sec.

Fig.18 Voltage waveform after using DPFC in time 0.5 to 0.8 sec

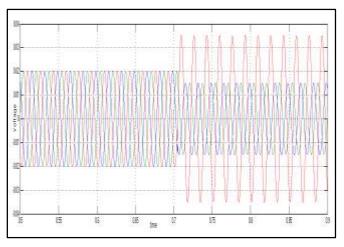

Here in the simulation we are taking the total time of 1.5 seconds and taking the waveforms of sag and its mitigation with different time limits and the voltages are pu voltages. First the sag due to fault is in the time between 0.3 to 0.5 seconds and source voltage dip is in the time of 0.7 to 0.9 seconds. Sag condition is mitigated by DPFC device and we get the constant voltage output waveform.

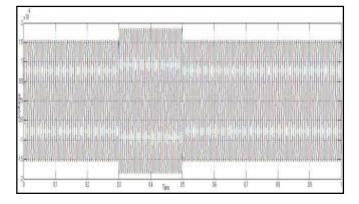

# MATLAB simulation of voltage swell condition

Fig. 19 MATLAB model for swell problem

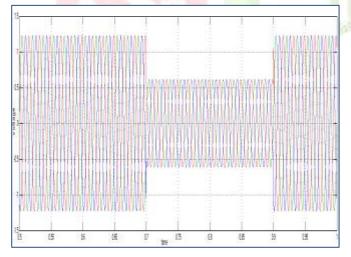

Fig 20 Waveform of voltage swell occurs by using circuit breaker in time 0.6 to 0.7 sec

Fig 21 Waveform of voltage swell by using circuit breaker in time 0.2 to 0.8 sec

Fig.22 Waveform of RMS value of voltage swell

# MATLAB simulation of voltage swell mitigation using DPFC

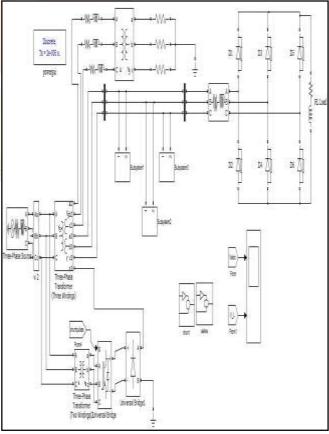

Fig.23 MATLAB simulation of voltage swell mitigation using DPFC

# Voltage waveform after using DPFC for swell mitigation

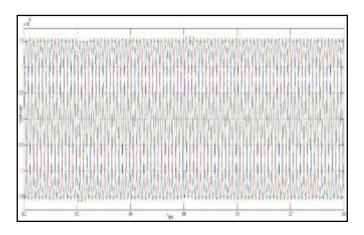

Fig.24 waveform of voltage swell source side

Fig. 25 wave form of voltage pulse during 0 to 0.5 second

Fig.26 wave form of constant output voltage after using DPFC

Fig.27 wave form of constant output voltage after using DPFC in time 0.2 to 0.8

Fig 28 waveform of RMS value of output voltage

# MATLAB simulation of voltage sag and swell condition with nonlinear load

Fig.29 Matlab model for sag and swell condition for nonlinear load

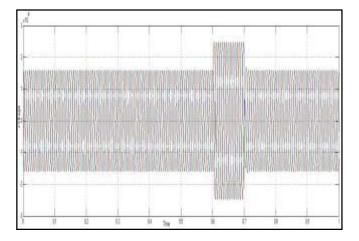

Here we are using a three-phase source and nonlinear load for creation of sag and swell and after that we can see the output waveform as below for one second of time.

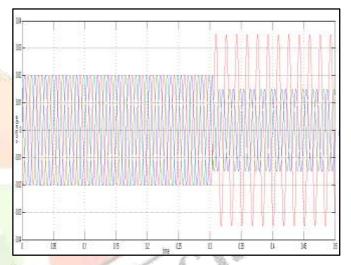

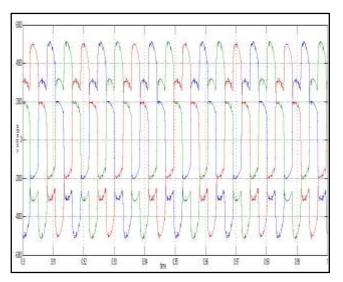

Fig.30 Load side voltage waveform for sag and swell condition for nonlinear load

# MATLAB simulation of voltage sag and swell mitigation for nonlinear load using DPFC

Fig.31 Matlab model for sag and swell mitigation using DPFC for nonlinear load

Fig.32 Load side voltage waveform for sag and swell condition after using DPFC for nonlinear load

#### Theory of DPFC for interconnected multi bus system

Fig.33 Three source ten bus system for example

Here we are going to discuss how to put DPFC for our real life interconnected system. Here we are taking ten bus system. If at any bus, fault is there at that faulty bus we will put DPFC at that bus.

The shunt converter puts at source side and three single phase converter puts in that transmission line. We can put multiple single-phase converter so that we can maintain the voltage.

#### Ratings and formula

Source:

Input voltage: 25 K volt Frequency: 60 Hz **Transformer**:

KVA rating: 250 MVA Output voltage: 25 KVA R=0.002pu, L=0.08pu Base KVA=25 KVA

Fault:

Fault resistance=0.67ohm (LLLG fault timer based)

Shunt transformer: KVA rating: 250 MVA Output voltage: 1 KVA R=0.002pu, L=0.08pu Series sub system: Capacitance: 2000\*10<sup>-6</sup> Load (3 phase)

R=0.1 ohm L=0.130 H

**Shunt converter:**

Initial constant value in to PI controller=0

Propotional gain (Kp) =0.1

Intrgral gain (Ki) =1

Constant output voltage =1 pu

Source for swell:

V=11k\*1.414=15556 V

Transformer for swell:

Step up 11kv in to 115 kv

Step down in to 11 kv

dqo to abc transformation

$Va = Vd \sin wt + Vq \cos wt + Vo$

$$Vb = Vd \sin(wt - \frac{2\pi}{3}) + Vq \cos(wt - \frac{2\pi}{3}) + Vo$$

$$Vc = Vd\sin(wt + \frac{2\pi}{3}) + Vq\cos(wt + \frac{2\pi}{3}) + Vo$$

abc to positive ,negative and zero sequence transformation

$$V1 = \frac{1}{3}(Va + \alpha Vb + \alpha^2 Vc)$$

$$V2 = \frac{1}{3}(Va + \alpha^2 Vb + \alpha Vc)$$

$$V3 = \frac{1}{3}(Va + Vb + Vc)$$

# **CONCLUSION**

The power quality enhancement of the power transmission systems is a vital issue in power industry. In this study, the application of DPFC as a new FACTS device in the voltage sag and swell mitigation of a system composed of a three-phase source connected to a R-L load through the parallel transmission lines is simulated in

Matlab/Simulink environment. The voltage dip is analyzed by implementing a three-phase fault close to the system load. The obtained simulation results show the voltage sag and voltage swell. We can mitigate the voltage sag and swell problem using DPFC device in this paper and shows that which device is better for those power quality problems.

**REFERENCES**

- (1) "Power Quality Improvement and Mitigation Case Study Using Distributed Power Flow Controller" By Ahmad Jamshidi, S. MasoudBarakati, and Mohammad MoradiGhahderijani ECE Department, University of Sistan and Baluchestan, Iran

- (2) "Power Quality Improvement In Transmission Systems Using DPFC" By S.Divya, (PG student) and U. Shyamala (Asst. Professor) Dept. of Electrical and Electronics, M.Kumarasamy college of engineering, Karur, India.

- (3) "A FACTS DEVICE: Distributed Power Flow Controller (DPFC)" by Zhihui Yuan, Student Member, IEEE, Sjoerd W. H. de Haan, Member, IEEE, Jan Braham Ferreira, Fellow, IEEE, and DaliborCvoric, Student Member, IEEE

- (4) "Improvement of Power Quality by Using DPFC" By S. Ashok Kumar and N. VishaliM.Tech, Department of EEE, JNTP University Pulivendula, A.P, India

- (5) "Voltage sag and swell mitigation using DPFC and improve power quality" by P.HimaBindu, V.LavanyaDept. of EEE Loads Institute of Engg. And Technology, A.P,INDIA

- (6) "Mitigation of Voltage sag and swell using Distributed Power Flow Controller" By P.Rajasekhar, Ch.NarayanaAssistant Professor, Dept. of EEE S.V.P.C.E.T Puttur, chittore, Andhra Pradesh IndiaP.G Student, Dept.of EEE, M.Tech (E.P.S) S.V.P.C.E.T Puttur, chittore Andhra Pradesh India

- (7) "Simulation of Distributed Power Flow Controller (DPFC)" By SarimallaPedakotitaiah and Santosh A.

- (8) "Harmonics reduction and power quality improvement by using DPFC" By Akula N.V.V Rajasekhar, Assistant Professor of EEE departmen,ST. Ann's College of engineering and technology, Chirala, Andhra Pradesh and Mamidi Naveen Babu,Assistant Professor of EEE department ST. Ann's College of engineering and technology, Chirala, Andhra Pradesh.