# High Speed Full Adder Design with Analog Switch Level Restoration Technique.

<sup>1</sup>Srikanth Koniki, <sup>2</sup>Utlapalli Somanaidu, <sup>3</sup>Shashikanth Reddy, <sup>4</sup>Nehru K

<sup>1</sup>Assistant Professor, <sup>2</sup>Assistant Professor, <sup>3</sup>Assistant Professor, <sup>4</sup>Professor

<sup>1</sup>Department of Electronics and Communication Engineering, <sup>1</sup>Prakasam Engineering College, Kandukur, India

<sup>2,3,4</sup>Institute of Aeronautical Engineering, Hyderabad, India

*Abstract:* In the field of very large scale integration (VLSI) till date there are a plenty of 1-bit full adder. In this paper we have implementation the comparative analysis of 16 transistors Transmission function full adder circuit (TFA) and 20 transistors modified conventional full adder circuit. And we compare with different pass transistors for the decrease the count of transistors considering various elements in like power, delay and power delay product. These constraints are calculated by using cadence virtuoso platform in 180nm Technology. The full adder is part of the processor we can increase the n-bit full adder to implement the complex circuits.

Index Terms - Full adder circuits, cadence virtuoso tool and Transistor count.

## I. INTRODUCTION

Many paper are in the VLSI filed most of publication in low power consumption and count of the transistors decrease the area of the chip. So In this paper a brief description of Transmission full adder and modified conventional full adder. But at the circuit level an optimized design is desirable have less number of transistor and decreasing the power and reducing the delay. There are different types of CMOS technology in vlsi like Transmission gate (TG), Pass-transistors logic (PTL), complementary pass transistors logic (CPL) dual rail domino logic and gate diffusion input (GDI) but all types have the pros and cons. The threshold problems are logic 1 is not the value of  $v_{dd}$  and logic 0 is not value of zero. The threshold problems are reduced by using different levels of restoration factors. Many in this paper suggests a classification and clarifies the circuits of full adder single-bit adders based on 16 transistors and 20 transistors modified conventional CMOS full adder with reduce the low power and high speed. The comparative analysis has been carried out according to the simulation results of single-bit circuits are based on them taking into account the input currents at the same output load [1]. Recommendations on the use of circuits are given below.

## Transmission gate full adder design

The Implementation of this full adder is realized by Reusing the C<sub>out</sub> term in the sum term as a common sub expression. The logic function for this implementation are,

$$sum = A \bigoplus B \bigoplus C_{in}$$

$$C_{out} = (A \bigoplus B).C_{in} + A.B$$

1

2

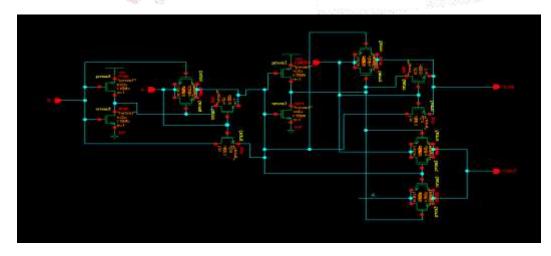

Figure1: Transmission Function Full adder (TFA)

In order to further simplify the full adder which is the fundamental unit of the arithmetic unit, a CMOS full adder based on the transmission function theory called as the transmission function adder (TFA), was developed as shown in above figure 1. The TFA shown in above figure consists of 16 transistors [2] and dissipates less power than that of the conventional CMOS full adder.

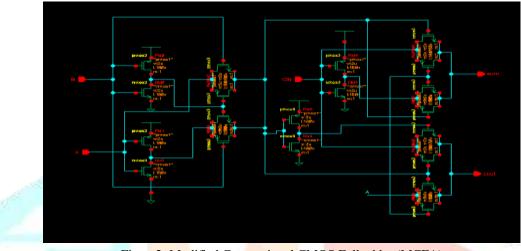

The below circuit shows the modified conventional CMOS full adder in the figure 2 consists of 20 transistors are required compare to above transmission full adder the with increase of two transistors more it decrease the power and delay. The main problem of this modified circuit is its critical delay that limits the performance of the system. This problem is worse when two or more full adder circuit are cascaded together to perform multiple-bit addition. With drain diffusion area and Source diffusion area of NMOS 440f and PMOS 480f. Different parameters are differing in below the table.

II.

### **Design of conventional CMOS Full adder**

Figure2: Modified Conventional CMOS Full adder (MCFA)

In the cmos adder architectures multiple bit addition can be as simple as connecting several full adders in series or it can be more complex [3]. The 20 transistors full adder was designed using a transmission gate it produced for both the sum and carry with proper polarity the xnor and xor are used to generate the sum and cin again cin input is multiplexed which can simultaneously inputs are used to generate sum and cout

$$Cout = A.B+Cin.(A+B)$$

Sum = A.B.Cin + (A+B+CIn).Cout bar

$$= A.B.Cin + (A+B+Cin). (A.B.+Cin.(A+B)) bar$$

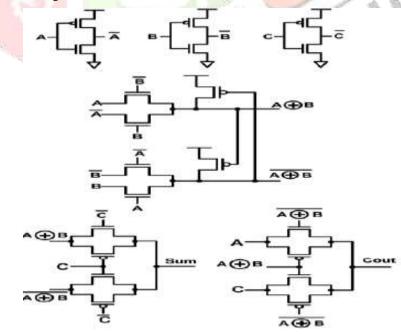

The Equivalence gates of (XNOR/XOR) are realized using full swing restored complementary MCFA and sum and count expressions are realized in the below circuit diagram these are alternate structures of full adders are as shown below

Figure3: Alternate circuit diagrams of Full adder

The different full adder circuits have the two states ON state and OFF state when all inputs are zero the SUM and Cout will be zero when all inputs are high then the sum and carry are in High[4,5]. The truth table is shown below.

Table1: Truth table of a full adder

| Cin | А | В | SUM | Cout |

|-----|---|---|-----|------|

| 0   | 0 | 0 | 0   | 0    |

| 0   | 0 | 1 | 1   | 0    |

| 0   | 1 | 0 | 1   | 0    |

| 0   | 1 | 1 | 0   | 1    |

| 1   | 0 | 0 | 1   | 0    |

| 1   | 0 | 1 | 0   | 1    |

| 1   | 1 | 0 | 0   | 1    |

| 1   | 1 | 1 | 1   | 1    |

In the below table shows the default properties of transistor in cadence design tool[6] to decrease the power to the make the IC to low power vlsi we can make the concept of transistor sizing to implement the less power consumption to the system. The results are shown below for double pass transistor and complementary pass transistor, Transmission function full adder circuit and Modified Conventional CMOS Full adder.

| Tabel2: Properties of Transistor in cadence virtuoso tool |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

|                       | Model name                     | NMOS   | PMOS   |

|-----------------------|--------------------------------|--------|--------|

|                       | Length                         | 180n M | 180n M |

|                       | Total width                    | 2u M   | 2u M   |

| 1.0                   | Threshold                      | 800n M | 800n M |

| Con R                 | S/D metal width                | 400n M | 400n M |

| 0.000                 | Drain diffusion area           | 440f   | 480f   |

| 1                     | Source diffusion area          | 440f   | 480f   |

| and have a series     | Drain diffusion area periphery | 2.8u M | 2.8u M |

| and the second second | Source diffusion periphery     | 2.8u M | 2.8u M |

| 2.24                  |                                | 2005.0 |        |

Table3: Results For average power and average Delay

| S.No | Average Power        | Average Delay         |

|------|----------------------|-----------------------|

| TFA  | 696.0E <sup>-6</sup> | 47.78E <sup>-12</sup> |

| CPL  | 410.0E <sup>-6</sup> | 62.01E <sup>-12</sup> |

| DPL  | 248.0E <sup>-6</sup> | 28.15E <sup>-12</sup> |

| MCFA | 246.0E <sup>-6</sup> | 4.789E <sup>-12</sup> |

The simulation results are taken as reference from [19-23]. In the below table shows the default properties of transistor in cadence design tool[7-10] to decrease the power to the make the IC to low power vlsi we can make the concept of transistor sizing to implement the less power consumption to the system[8-15]. The results are shown below for double pass transistor and complementary pass transistor[16-18], Transmission function full adder circuit and Modified Conventional CMOS Full adder.

| Model name                     | NMOS   | PMOS   |

|--------------------------------|--------|--------|

| Length                         | 180n M | 180n M |

| Total width                    | 2u M   | 2u M   |

| Threshold                      | 800n M | 800n M |

| S/D metal width                | 400n M | 400n M |

| Drain diffusion area           | 440f   | 480f   |

| Source diffusion area          | 440f   | 480f   |

| Drain diffusion area periphery | 2.8u M | 2.8u M |

| Source diffusion periphery     | 2.8u M | 2.8u M |

Table3: Results For average power and average Delay

| s.no | Average Power                     | Average Delay                                                                                      |

|------|-----------------------------------|----------------------------------------------------------------------------------------------------|

| TFA  | 696.0E <sup>-6</sup>              | 47.78E <sup>-12</sup>                                                                              |

| CPL  | 410.0E <sup>-6</sup>              | 62.01E <sup>-12</sup>                                                                              |

| DPL  | 248.0E <sup>-6</sup>              | 28.15E <sup>-12</sup>                                                                              |

| ICFA | 246.0E <sup>-6</sup>              | 4.789E <sup>-12</sup>                                                                              |

|      | s.no<br>TFA<br>CPL<br>DPL<br>ICFA | TFA         696.0E <sup>-6</sup> CPL         410.0E <sup>-6</sup> DPL         248.0E <sup>-6</sup> |

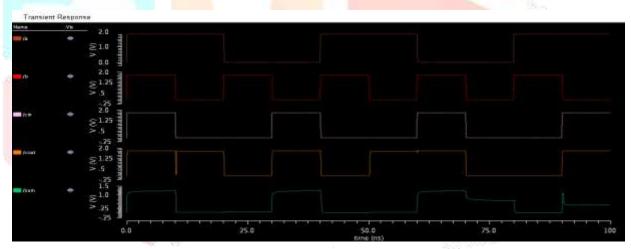

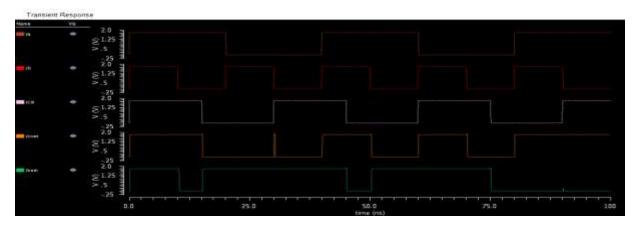

**Results:** The transient response output waves are eradicated by cadence virtuoso tool as shown in below

Figure4: TFA Wave Forms

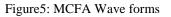

Figure6: DC-Characteristic of TFA

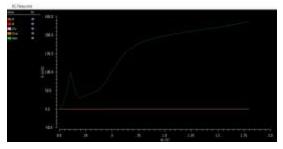

Figure7: DC-Characteristic of MCFA

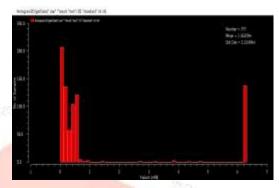

Figure8: average power histogram for MCFA

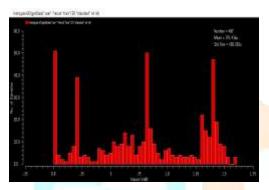

Figure9: average power histogram forTFA

Histogram for the modified conventional full adder diagram the indication of mean and standard Deviation by taking the x-axis on values mW and on Y-axis No of samples are taken

## III. Conclusion

In this paper we are completed on cadence virtuoso tool and calculated the power and delay the circuit to the count of the transistor and the performance is calculated with several 1 bit full adder circuits. The full adder architectures are using in the microprocessor for the resulting the high performance

#### REFERENCES

[1] A. M. Shams and M. Bayoumi, 1999. Performance evaluation of 1-bit CMOS adder cells, in Proc. IEEE ISCAS, Orlando, FL, 27 30.

[2] K. Yano, et al 1990. A 3.8 ns CMOS 16x16-b multiplier using complementary pass-transistor logic, IEEE J. Solid-State Circuits, 388-395.

[3] Mariano Aguirre-Hernandez and Monico Linares-Aranda, 2011. CMOS Full-Adders for Enery Efficient Arithmetic Applications, (EEE Tran. On VLSI Systems, 718-721.)

[4] M. Suzuki, et al 1993. A 1.5 ns 32-bit CMOS ALU in double pass-transistor logic, IEEE J. Solid-State Circuits, 1145-1150.

[5] N. Weste and K. Eshraghian, 1998. Principles of CMOS VLSI Design, A System Perspective. Reading, MA: Addison-Wesley, chapter. 5.

[6] R. Zimmerman and W. Fichtner, 1997. Low-power logic styles: CMOS versus pass-transistor logic, IEEE J. Solid-State Circuits, 1079-1090.

[7] S. Agarwal, V. K. Pavankumar, and R. Yokesh,2008. Energy-efficient high performance circuits for arithmetic units, in Proc. 2nd Int. Conf. VLSI Des, 371-376.

[8] T. Bhagyalaxmi, S. Rajendar, Y. Pandu Rangaiah, 2014, Performance Analysis of Alternative Adder Cell Structures using Clocked and Non-Clocked Logic Styles at 45nm Technology, Proc. IEEE ICACCI, New Delhi, 620-623.

[9]Nehru, K., Shanmugam, A., & Thenmozhi, G. D. (2012, March). Design of low power ALU using 8T FA and PTL based MUX circuits. In Advances in Engineering, Science and Management (ICAESM), 2012 International Conference on(pp. 145-149). IEEE.

[10]Nehru, K., & Shanmugam, A. (2014). Design of high-performance low-power full adder. International Journal of Computer Applications in Technology, 49(2), 134-140.

[11] Nehru, K., Shanmugam, A., Deepa, S., & Priyadarshini, R. (2010). A shannon based low power adder cell for neural network training. International Journal of Engineering and Technology, 2(3), 258.

[12] Nehru, K., & Linju, T. T. (2017). Design of 16 Bit Vedic Multiplier Using Semi-Custom and Full Custom Approach. Journal of Engineering Science & Technology Review, 10(2).

[13]Nehru, K., Babu, M. R., Sravana, J., & shashikanth Reddy(2016, January). Performance analysis of low power and high speed 16-Bit CRC Generator using GDI technique. In Advanced Computing and Communication Systems (ICACCS), 2016 3rd International Conference on (Vol. 1, pp. 1-5). IEEE.

[14] Kandasamy, N., Telagam, N., & Devisupraja, C. (2018). Design of a Low-Power ALU and Synchronous Counter Using Clock Gating Technique. In *Progress in Advanced Computing and Intelligent Engineering* (pp. 511-518). Springer, Singapore.

[15] Khadir, Mohammad, K. Nehru, T. Nagarjuna, and G. Shruthi. "INVESTIGATION AND ANALYSIS OF LOW POWER MODIFIED 14T ADDER AND 20T ADDER CIRCUITS." (2017).

[16] Nehru, K., T. Nagarjuna, and G. Vijay. "Comparative Analysis of CNTFET and CMOS Logic based Arithmetic Logic Unit." *JOURNAL OF NANO-AND ELECTRONIC PHYSICS* 9, no. 4 (2017).

[17] Nagarjuna, T., K. Nehru, A. Usharani, and L. Raviteja. "Design and Development of Coded OFDM based Digital Audio Broadcasting System using Concatenated Convolutional Turbo Codes."

[18] Telagam, N., Kandasamy, N., & Nanjundan, M. (2017). Smart Sensor Network Based High Quality Air Pollution Monitoring System Using Labview. *International Journal of Online Engineering (iJOE), 13*(08), 79-87.

[19] Telagam, N., Nanjundan, M., Kandasamy, N., & Naidu, S. (2017). Cruise Control of Phase Irrigation Motor Using SparkFun Sensor. *International Journal of Online Engineering (iJOE)*, 13(08), 192-198.

[20] Gantala, Anil, K. Nehru, Nagarjuna Telagam, P. Anjaneyulu, and Dasari Swathi. "Human Tracking System using Beagle BoardxM." *International Journal of Applied Engineering Research* 12, no. 16 (2017): 5665-5669.

[21] Telagam, Nagarjuna, Nehru Kandasamy, Menakadevi Nanjundan, and T. S. Arulanandth. "Smart Sensor Network based Industrial Parameters Monitoring in IOT Environment using Virtual Instrumentation Server." *International Journal of Online Engineering (iJOE)* 13, no. 11 (2017): 111-119.

[22] Kandasamy, Nehru, Nagarjuna Telagam, Seshagiri Rao VR, and T. S. Arulananth. "Simulation of Analog Modulation and Demodulation Techniques in Virtual Instrumentation and Remote Lab." *International Journal of Online Engineering (iJOE)* 13, no. 10 (2017): 140-147.

[23] Telagam, N., & Kandasamy, N. (2017). Low Power Delay Product 8-bit ALU design using decoder and data selector. *Majlesi* Journal of Electrical Engineering, 12(1).