ISSN: 2320-2882

## INTERNATIONAL JOURNAL OF CREATIVE **RESEARCH THOUGHTS (IJCRT)**

An International Open Access, Peer-reviewed, Refereed Journal

# Design And Performance Analysis Of Subsystem **Components Of Risc Processor**

<sup>1</sup>G Nandan Kumar Rao, <sup>2</sup>Dr. Jeeru Dinesh Reddy <sup>1</sup>Student, <sup>2</sup>Assistant Professor <sup>1</sup>Department of ECE <sup>1</sup>B.M.S College of Engineering, Bengaluru, India

Abstract: This report presents the design and performance analysis of key subsystem components in a 16-bit Reduced Instruction Set Computing (RISC) processor. The study focuses on three primary adder implementations: Ripple Carry Adder (RCA), Carry Look-Ahead Adder (CLA), and Carry Select Adder (CSA). These adders play a vital role in defining the arithmetic processing capabilities of the RISC processor. The project evaluates the impact of each adder architecture on critical performance metrics, including execution speed, area utilization, and power consumption. Simulations were conducted using Xilinx ISE, and performance was measured to assess the efficiency of each adder in various scenarios. Results indicate that while the CLA provides superior speed due to minimized carry propagation delays, the RCA excels in space efficiency, making it more suitable for compact designs. The CSA offers a balanced performance between speed and power efficiency, making it a viable option for high-performance computing tasks. Overall, the design and analysis provide valuable insights into the tradeoffs between speed, area, and power consumption in processor architecture, leading to an optimized RISC processor design

Index Terms: RISC - Reduced Instruction Set

### I. INTRODUCTION

Reduced Instruction Set Computing (RISC) is a type of computer architecture that emphasizes a small, highly optimized set of instructions. Its primary goal is to simplify instruction execution by using fewer fundamental operations, contrasting with Complex Instruction Set Computing (CISC), which uses a more extensive instruction

Key characteristics of RISC include a Simplified Instruction Set, which consists of basic operations for easier decoding and execution. Uniform Instruction Format and Load/Store Architecture simplify fetching, decoding, and memory operations. Register Usage is prominent, reducing memory access for improved performance. Execution breaks down instruction processing into stages for simultaneous execution. RISC processors also use Hardwired Control Units, enhancing speed through direct control signal generation, and their design favors Compiler Optimization for efficient code execution

A 16-bit RISC processor handles 16-bit data chunks and follows the core principles of RISC. It uses a simplified instruction set for efficient single-cycle execution

With Registers reducing memory access, the processor improves performance. The Load/Store Architecture ensures operations occur in registers, while Fixed-Length Instructions allow faster execution and decoding. The processor's design also focuses on Low Power Consumption, suitable for embedded and low-power applications.

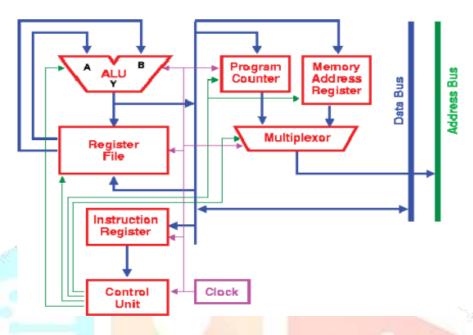

ALU- Arthematic and Logical UnitThe ALU performs arithmetic and logical operations. It takes input from the instruction's opcode and operands, processing them and storing results in registers.

Register Bank: The register bank stores intermediate data, providing a space for the ALU to store rsults. The Z-Flag indicates operation success or failure, and registers improve efficiency in memory based data operations CONTROL UNITS AND REGISTERS

Instruction Register (IR): Holds the instruction to be executed. The Control Unit decodes the opcode, retrieves operands, and executes the instruction with the help of timing signals.

Program Counter (PC): The PC points to the next instruction in memory, ensuring smooth instruction flow in the processor

Memory Address Register (MAR): The MAR holds the memory address for the current instruction, loading instructions into

Multiplexer (MUX): The multiplexer selects inputs and provides a single output, controlling data flow within the processor

Ripple Carry Adder (RCA):

performs basic arithmetic, sequentially processing bits and carry-outs. Its simplicity and space-efficiency make it ideal for a 16-bit processor.

Carry Look-Ahead Adder (CLA):

CLA precomputes carry signals to reduce delays, significantly improving arithmetic performance in the 16-bit processor

Carry Select Adder (CSA):

CSA parallelizes carry paths, optimizing speed and efficiency, making it a vital part of the processor's arithmetic unit

#### II. PROBLEM STATEMENT

The project aims to address the critical challenge of optimizing the design and performance of a 16-bit Reduced Instruction Set Computing (RISC) processor by employing distinct adder datapath logic cells. The specific focus lies on three primary adder implementations: Ripple Carry Adder (RCA), Carry Look- Ahead Adder (CLA), and Carry Select Adder (CSA). Each adder logic cell introduces unique characteristics influencing aspects such as execution speed, area utilization, and power consumption. The challenge is to comprehensively investigate the impact of these varied adder datapath logics on the overall efficiency of the 16-bit RISC processor.

### III. OBJECTIVE

### Define RISC ISA

The objective is to develop a streamlined RISC Instruction Set Architecture (ISA) that prioritizes simplicity and efficiency. This involves creating a minimal set of instructions that can perform essential operations effectively while minimizing complexity. A reduced instruction set is expected to enhance the processor's performance, optimize resource use, and simplify programming. The goal is a compact ISA that executes instructions rapidly,

ultimately improving processing speeds and overall processor performance

### Implement Different Adders:

Enhancing arithmetic capabilities by integrating various adder architectures is another key objective. The processor will include ripple carry adders, carry select adders, and Wallace tree multipliers, each offering specific advantages in terms of speed, efficiency, and area utilization. Incorporating these diverse adder logics will enable the processor to handle arithmetic operations efficiently, supporting a range of computational tasks.

#### **Ensure Correctness:**

Verifying the processor design rigorously is essential for reliability. Extensive simulation and testing will assess all functionalities, including instruction behavior, data handling, and component interactions. This verification phase ensures early identification of potential issues, resulting in a robust and dependable processor design

#### IV. METHODOLOGY

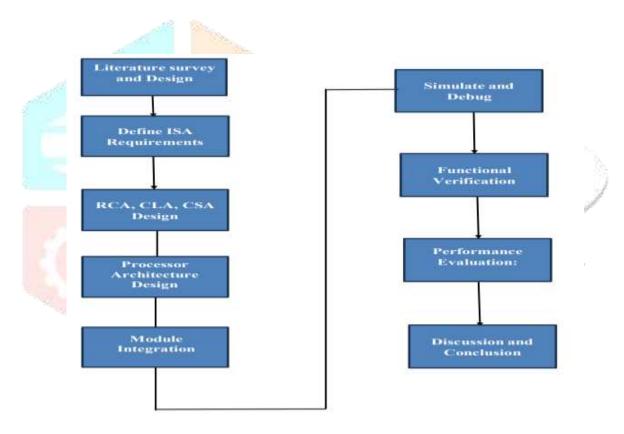

This study outlines the development of a RISC processor design using optimized adder circuits, structured into nine distinct phases. First, a Literature Survey was conducted to assess current RISC processor designs and adder circuits like RCA, CLA, and CSA, forming the foundation for our design approach. Second, ISA Requirements were defined, outlining instruction formats, addressing modes, and essential operations, customized to support the integrated adders.

The RCA, CLA, and CSA Design phase focused on developing the adders, with RCA for simplicity, CLA for speed enhancement through carry prediction, and CSA for efficient multi-operand addition. In Processor Architecture Design, the ISA and adder designs were integrated into the processor's core components—ALU,

control unit, registers, and data paths. Model Integration followed, where the adders were connected to enable seamless data flow and arithmetic processing within the architecture.

The sixth phase involved Simulation and Debugging to test the processor's functionality and identify errors, ensuring alignment with design objectives. Functional Verification was then performed to confirm the processor's compliance with ISA specifications, verifying the accuracy of RCA, CLA, and CSA operations. During Performance Evaluation, metrics like speed and efficiency were measured to assess the processor's handling of arithmetic operations with different adders. Finally, in Discussion and Conclusion, results were summarized, addressing challenges, design success, and suggesting future enhancements for improved processor performance

### v. **RESULTS**

The results section presents the outcomes of implementing the RISC processor design, Using Ripple carry adder, Carry Look Ahead Adder and Carry select Adder. This includs performance metrics and functionality validation. This analysis evaluates the processor's efficiency by highlighting Area, Time and Power consumed by respective adders

### 1. Schematic Results

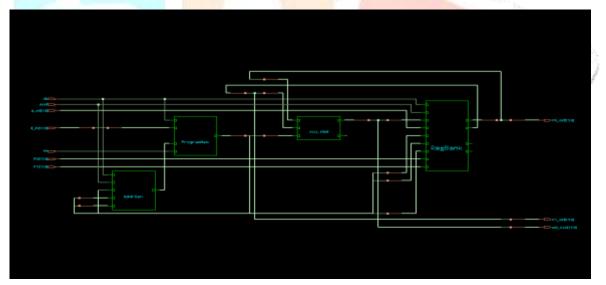

Fig1.1: Overall View

Fig 1.2 : Address Generator

The following image illustrates the address generator of the RISC processor, which was synthesized to optimize address computation and enhance overall processing efficency

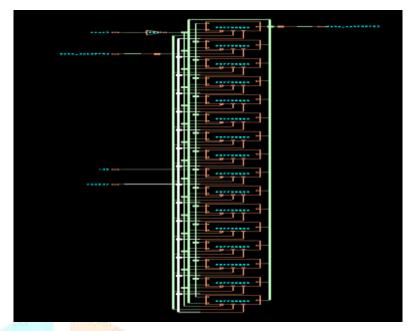

Fig 1.3: Register Bank

The image depicts the register bank of the RISC processor, showcasing the synthesized design that facilitates efficient data storage and retrieval across the processor's execution stages

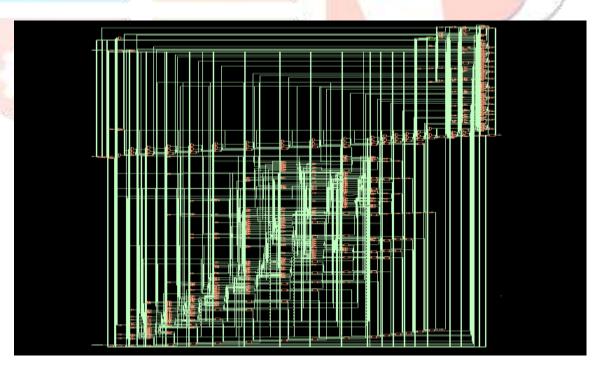

Fig 1.4: Arthematic and Logical Unit

Figure shows the Arithmetic Logic Unit (ALU) of the RISC processor, illustrating its synthesized design that performs critical arithmetic and logical operations essential for Processing instructions

### 2. Simulation Results

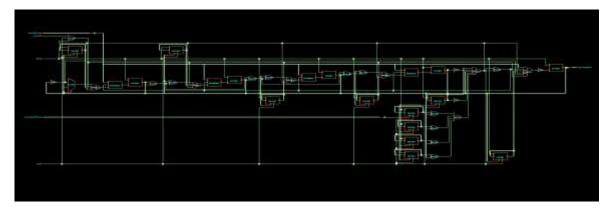

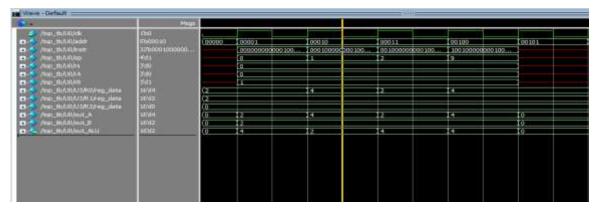

Fig 2.1 Simulation Result of Risc Processor

### 3. Area and Power Results

### Risc

Fig 3.1 Area and Power of Risc

Total Area: 9705.618 um<sup>2</sup>

Total Power (Leakage): 517.686 nW

### **RCA** (Ripple Carry Adder)

Fig 3.2 Area and Power of RCA

Total Area: 9753.156 um<sup>2</sup>

Total Power (Leakage): 519.302 nW

### CLKA(Carry Look Ahead Adder)

Fig 3.3: Area and Power of CLKA

Total Area: 9829.764 um<sup>2</sup>

Total Power (Leakage): 524.236 nW

d696

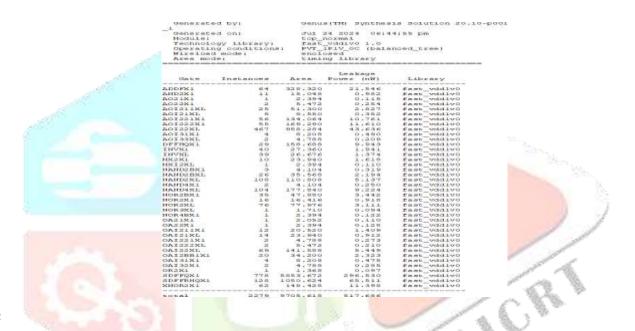

### • **CSLA** (Carry Select Adder)

| Cenerate    | of few          | Ownu        | ection synthese            | as returned z   |  |

|-------------|-----------------|-------------|----------------------------|-----------------|--|

| 1           |                 |             |                            |                 |  |

| Ginecoun    | rot men         |             | (Fe3. 24. 2024 04:25:35 pm |                 |  |

| secdule:    |                 | top.        |                            |                 |  |

|             | by library:     |             | wddlw0 l:0                 |                 |  |

|             | of month-thousa |             | IPIV OF (Bale              | and the same of |  |

| Witeloed    |                 |             | enclosed<br>timing library |                 |  |

| Arma mod    | im t            | 1.584.51    |                            |                 |  |

|             |                 |             |                            |                 |  |

|             |                 |             | Leakeur                    |                 |  |

| 00.50       | Instances       | Aces        | Forms: (DW)                | Library         |  |

| 0.856.9     | 64              | 328-320     | 22,448                     | East wasted     |  |

| ADDRECT.    | 4.0             | 100.576     | 12,705                     | fest vocivo     |  |

| DODGE &     |                 | 4.104       | 0.256                      | Case while's    |  |

| 12055       | -               | 0.972       | 0.252                      | Fast Vocativo   |  |

| TRIENT      | 2.4             | 49.240      |                            | fest vddiv0     |  |

| INCK!       | 3               | 3.420       | 0.1117                     | East whiled     |  |

| SERVING     | 16.22           | 124-488     |                            | feet vacivo     |  |

| TREST       | 67              | 187,789     | 12,797                     | fast widly)     |  |

| THEFT.      | 471             | me4.402     | 43,955                     | FARS WESTYS     |  |

| 120001      | - 4             | 46.756      |                            | feet wastwo     |  |

| LIKE GOODS. | 0               | 21.008      |                            | fam whiles      |  |

| FIREDOC L   | 29              | 155,665     | Nr . 10-10 (8)             | fast vactvo     |  |

| V363        | 5.7             | 25,300      | 1,700                      | fast whiles     |  |

| VXII        | 3.0             | 20.820      |                            | fines vehillard |  |

| 200.3       | 3.2             | 79,002      |                            | fast vddivo     |  |

| ISNL        | 1.7             | 40 - 690    |                            | fast wddiwd     |  |

| RECURSOS A  |                 | 4-104       |                            | East whitivo    |  |

| NEGREE      | 14              | 19,152      |                            | fest_widivo     |  |

| RDG-KL      | 11.6            | 117,990     |                            | fare wedstwo    |  |

| CXWellin    |                 | 1.710       |                            | FRAS WEGSTON    |  |

| ND+BBKL     | 1               | 3.029       |                            | fast_widivo     |  |

| SED-EBXT.   | 1               | 2 - 394     |                            | fast vestion    |  |

| MENSA       |                 | 10.380      |                            | PARE VEGIVO     |  |

| SFD4NL      | 109             | 100,390     |                            | East widly0     |  |

| BURS 1      | 21              | 28.728      | 2.028                      | East whilve     |  |

| REEL        | 16              | 36.916      | 0.916                      | fast vadivo     |  |

| DESKI.      | 72              | 73-672      | 81879                      | feet william    |  |

| OR SELECT   |                 | 1,740       |                            | FASE WESTVO     |  |

| 98.981      | 1               | 1,710       |                            |                 |  |

| 122E2       | 1               | 2.004       | 0,101                      | fast_vddlv0     |  |

|             | 11              | 18.810      | 1.276                      | ERSC_AGGIAG     |  |

| 122.183     |                 |             |                            |                 |  |

| I 22 NI.    | 51              | 18,810      | 0.672                      | fast_widlw0     |  |

| THERE       |                 | 137-464     |                            | Enan waditod    |  |

| X ZBB LX1   | 9               | 0-550       | 0.575                      | ERRE WARTAN     |  |

| 130×1       | h.              | 2.394       | 9,136                      | fast_widlw0     |  |

| 230         | 2.1             | 31.464      | 2.686                      | EAST WEST-OC    |  |

| PPOKI       | 710             | 5.053 - 472 | 296:500                    | feat_widing     |  |

| E.E.ROHOSCI | 13.6            | 1080-624    | 68-55-4                    | East_wddlw0     |  |

| CHURY       | 4.0             | 114,912     | 0.010                      | fast_vddivo     |  |

| u = 2       | 2322            | WHAN . NO.  | 534,536                    |                 |  |

|             |                 |             |                            |                 |  |

Fig 3.4 Area and Power of CSLA

Total Area: 9919.368 um<sup>2</sup>

Total Power (Leakage): 531.536 nW

### 4. Delay Output

RISC: In the RISC processor design the critical path delay from the first register to the last register measures 1215 ps, reflecting the overall time required for data to propagate through the entire pipeline of the processor.

RCA: In the RISC processor design utilizing a Ripple Carry Adder, the critical path delay from the first register to the last register measures 1300 ps, reflecting the overall time required for data to propagate through the entire pipeline of the processor.

CLKA: In contrast, when implementing the Carry Select Adder with an optimized design, the delay from the first to the last register is reduced to 1290 ps, demonstrating an improvement in the data propagation time through the processor's pipeline

In the RISC processor design using a Carry Select Adder, the delay from the first to the last register is 1300 ps, indicating the time required for data to traverse the full pipeline of the processo

### VI. CONCLUSION

This study evaluated the performance of an Ideal RISC Processor and three distinct adder architectures—Ripple Carry Adder (RCA), Carry Look-Ahead Adder (CLA), and Carry Select Adder (CSA)—analyzing their impact on total area, power (leakage), and critical path delay. The Ideal RISC Processor emerged as the most compact and power-efficient, occupying the smallest area at 9705.618 µm² and exhibiting the lowest leakage power of 517.686 nW. Each adder type increased the processor's area slightly, with the CSA occupying the largest area at 9919.368 µm². Power consumption followed a similar trend, where the CSA exhibited the highest leakage at 531.536 nW, indicating a trade-off between performance and resource utilization across different adder architectures

d697

offs. The Ideal RISC Processor achieved the shortest delay at 1215 ps, reflecting its efficient design without additional adder complexities. Among the adders, the CLKA proved the fastest, with a minimal delay of 1290 ps, whereas both the RCA and CSA had a delay of 1300 ps. This suggests that while the CLKA slightly increases the processor's area and power, it provides an optimal balance of speed and efficiency.

### **Final Conclusion**

The corrected delay values underscore that the Ideal RISC Processor is the best choice for applications requiring minimal area, power, and delay, confirming its optimality in terms of size and efficiency. The CLA, with its reduced critical path delay, presents the most efficient adder choice, balancing speed with moderate area overhead. In contrast, the RCA and CSA show equal delay, but the CSA demands significantly more area and power, rendering it less favorable in contexts where compactness and low leakage are critical. This study concludes that while each adder architecture offers unique advantages, the Ideal RISC Processor provides the most balanced performance, with CLKA as a viable option for designs prioritizing delay over area.

### .Comparison Table

| 9970             |          |        |         |

|------------------|----------|--------|---------|

| Parameters       | Area     | Delay  | Power   |

| RISC Processor   | 9705.618 | 1215ps | 517.686 |

|                  | um²      | ĺ l    | nW      |

| RCA(Ripple carry | 9753.156 | 1300ps | 519.302 |

| adder)           | um²      | 19     | nW      |

| CLKA(Carry       | 130      | 1290ps | 524.236 |

| Look Ahead       | 9829.764 |        | nW      |

| Adder)           | um²      |        |         |

| CSLA (Carry      | 9919.368 | 1300ps | 536     |

| Select Adder)    | um²      |        |         |

|                  |          |        | 1,000   |

### VII. ACKNOWLEDGEMNT

We would like to acknowledge thank everyone and Assistant Professors of Dr. Jeeru Dinesh Reddy Dept. of ECE BMS college of Engineering for his support in designing this project

### REFERENCES

- [1]. P. Trivedi and R. P. Tripathi, "Design & analysis of 16 bit RISC processor using low power pipelining," International Conference on Computing, Communication & Automation, Greater Noida, India, 2020, pp. 1294-1297, doi: 10.1109/CCAA.2015.7148575

- \[2]. R. Bhat, D. Pandey, F. Ahmad and P. Gupta, "Analysis and Optimization of 16-bit RISC Processor and 32-bit MIPS Processor: A Review," 2023 3rd International Conference on Intelligent Technologies (CONIT), Hubli, India, 2023, pp. 1-6, doi: 10.1109/CONIT59222.2023.10205898.

- [3]. C. Venkatesan, M. T. Sulthana, M. G. Sumithra and M. Suriya, "Design of a 16-Bit Harvard Structure RISC Processor in Cadence 45nm Technology," 2019 5th International Conference on Advanced Computing &

Communication Systems (ICACCS), Coimbatore, India, 2019, pp. 173-178, doi: 10.1109/ICACCS.2019.8728479.

- [4]. S. S. Khairullah, "Realization of a 16-bit MIPS RISC pipeline processor," 2022 International Congress on Human-Computer Interaction, Optimization and Robotic Applications (HORA), Ankara, Turkey, 2022, pp. 1-6, doi: 10.1109/HORA55278.2022.9799944

- [5]. 8A. P. Singh, A. Rai, A. Rajput, P. C. Joshi and A. Prakash, "Design and Analysis of High Speed RISC Processor Using Pipelining Technique," 2022 4th International Conference on Advances in Computing, Communication Control and Networking (ICAC3N), Greater Noida, India, 2022, pp. 1642-1645, doi: 10.1109/ICAC3N56670.2022.10074423

- [6]. B. Ramkumar and H. M. Kittur, "Low-Power and Area-Efficient Carry Select Adder," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 20, no. 2, pp. 371-375, Feb. 2012, doi: 10.1109/TVLSI.2010.2101621

- [7]. Y. Xu et al., "Towards Developing High Performance RISC-V Processors Using Agile Methodology," 2022 55th IEEE/ACM International Symposium on Microarchitecture (MICRO), Chicago, IL, USA, 2022, pp. 1178-1199, doi: 10.1109/MICRO56248.2022.0008

- [8]. A. -S. Gheorghe and C. Burileanu, "Savage16 16-bit RISC architecture general purpose microprocessor," CAS 2010 Proceedings (International Semiconductor Conference), Sinaia, Romania, 2010, pp. 521-524, doi: 10.1109/SMICND.2010.5650480

- [9]. N. A. Gudala, T. Ytterdal, J. J. Lee and M. Rizkalla, "Implementation of High Speed and Low Power Carry Select Adder with BEC," 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, MI, USA, 2021, pp. 377-381, doi: 10.1109/MWSCAS47672.2021.9531750.

- [10]. M. Johns and T. J. Kazmierski, "A Minimal RISC-V Vector Processor for Embedded Systems," 2020 Forum for Specification and Design Languages (FDL), Kiel, Germany, 2020, pp. 1-4, doi: 10.1109/FDL50818.2020.9232940.

- [11]. Mamun B, Shabiul I. and Sulaiman S, "A Single Clock Cycle MIPS RISC Processor Design using VHDL

- [12]. J. C. Wright et al., "A Dual-Core RISC-V Vector Processor with On-Chip Fine-Grain Power Management in 28-nm FD-SOI," in IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, vol. 28, no. 12, pp. 2721-2725, Dec. 2020, doi: 10.1109/TVLSI.2020.3030243.

- [13]. M. Cavalcante, F. Schuiki, F. Zaruba, M. Schaffner and L. Benini, "Ara: A 1-GHz+ Scalable and Energy-Efficient RISC-V Vector Processor with Multiprecision Floating-Point Support in 22-nm FDSOI," in IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, vol. 28, no. 2, pp. 530-543, Feb. 2020, doi: 10.1109/TVLSI.2019.2950087.

- [14]. Á. B. de Oliveira et al., "Evaluating Soft Core RISC-V Processor in SRAM-Based FPGA Under Effects," in IEEE Transactions on Nuclear Science, vol. 67, no. 7, pp. 1503-1510, July 2020, doi: 10.1109/TNS.2020.299572