JCRT.ORG

ISSN: 2320-2882

## INTERNATIONAL JOURNAL OF CREATIVE RESEARCH THOUGHTS (IJCRT)

An International Open Access, Peer-reviewed, Refereed Journal

# A Low-Power 10T SRAM Cell Design With SAPON **And DTMOS Integration**

<sup>1</sup>M Sai Pavan Raj, <sup>2</sup>Mrs.Shaila V Hegde <sup>1</sup>Student, <sup>2</sup>Associate Professor <sup>1</sup>Department of ECE <sup>1</sup>B.M.S College of Engineering, Bengaluru, India

Abstract: This study delves into a 10T SRAM cell with little power incorporating two extra sleep transistors, distinguished by strong written and verbal stability. The 10T SRAM cell's core module houses these slumber gates as footers and header transistors. Using the Sapon method and DTMOS emerges as the optimal strategy to expand this approach for reduced power

consumption at 3.858 and latency at 1.503 The entirety of this design was simulated utilizing Tanner x 10 EDA's 16nm CMOS Technology.

Index Terms - SRAM, layered semiconductor, Schmitt activation circuit.

#### I. INTRODUCTION

Reducing power consumption has been crucial towards the creation of system-on-chips (SoCs), which find application in areas like bio-implants, smartphones, autonomous wireless sensors, and energy collection devices. These systems typically run on minimal energy sourced from batteries or renewable sources. S-RAM takes up a significant portion of the SoC, necessitating a focus on reducing SRAM energy usage as part of the broader goal to cut overall energy expenditure. The most efficient method to conserve energy involves lowering power consumption by diminishing the Vdd. As VDD decreases, power usage drops exponentially. Yet, this power reduction comes with drawbacks, such as increased delay times and elevated soft error rates (SERs), resulting in decreased operational efficiency. Within the sub-threshold voltage (Vth) zone, where VDD is less than Vth, delays escalate dramatically. Although this achieves ultra-low power levels, energy consumption spikes due to amplified static energy costs. Operating close to Vth, where VDD is just above Vth, enables significant power savings over super-Vth operations, alongside a notable reduction in delay compared to sub-Vth operations. Balancing power and delay in the near-Vth region is vital for minimizing energy usage. Near-Vth operation presents issues like soft errors caused by α-particles, increasing SER. To tackle this, In order to minimize multi-bit mistakes, a bit-interleaving scheme is used, a common issue in non-bit-interleaving setups. The near-Vth region also exhibits sensitivity to Vth variations in transistor currents, especially impacting SRAM cells due to the requirement for smaller transistors for higher density. In light of these considerations, we introduce ST 9T, obviating the need for a write-back mechanism. This design promises reduced use of energy relative to others while occupying a smaller cell area. Its standout features include the use of standard and Schmitt-trigger inverters in a cross-coupled structure for enhanced read stability, a unified bit-line structure for minimized energy use and space, and superior write performance achieved through a tailored Sapon technique in conjunction with the ST inverter write assist method.

## II. LITERATURE SURVEY

This research introduces tailored to meet the requirements for stable and energy-efficient SRAM in contemporary microprocessors functioning at reduced Vdds. We present a 12T Power Gated Schmitt Trigger SRAM cell architecture, with the goal of boosting read and write stability without necessitating supplementary peripheral circuits or control signals per cell. The design methodology employed SYNOPSYS Custom Designer for schematic development, layout, and result acquisition.

The design achieves the following notable outcomes:

A die size of 1.25 square millimeters. Power usage of 2.43 milliwatts.

Slack time of 31.45 nanoseconds.

The SRAM incorporates a 16-bit addressable word line and boasts a memory capacity of 512 bytes. It underwent simulation over an operating frequency spectrum of 25-200 MHz under a Vdd of 1V. Significantly, the primary contributor to power consumption in this fully customized design is identified as the banking and row decoders, indicating opportunities for optimization in subsequent versions. [1]. This study advances the initiative to create energy-efficient SRAM technologies appropriate for sophisticated microprocessor applications, underscoring the significance of pioneering cell designs and engineering approaches in attaining low-power operation without sacrificing performance or stability. [2]. The growing necessity to reduce power consumption in memory designs has led to a shift towards operating memories at lower Vdds. Research into sub-threshold operation for logic circuits indicates that minimal energy consumption is feasible in this regime. These findings imply a convergence for energy-limited applications where SRAM operates at sub-threshold voltages aligned with logic operations. Given that sub-threshold voltages offer limited space for large static noise margins (SNM), a deep comprehension of how various design choices and other factors influence SNM is essential. This study examines the dependence of SNM on sizing, V\_DD, temperature, and both local and global threshold variations for sub-threshold bit cells in a 65nm process [3]. Power management has emerged as the foremost design consideration for semiconductor engineers today. Despite Moore's Law continuing to add more transistors, power constraints now limit the practical application of these devices. Voltage scaling methods have gained traction as a means to decrease energy usage, with sub- threshold design marking the ultimate stage of voltage scaling. Though highly energy-efficient, sub-threshold design has remained confined to specialized applications due to significant performance drawbacks. This article delves into near-threshold computing (NTC), a design paradigm where the Vdd closely matches the transistor's threshold voltage. This approach combines the energy benefits of sub-threshold operation with improved performance and variability traits, making it suitable for a wide array of power-sensitive computing domains, from sensor networks to high-performance servers. The paper discusses the challenges hindering the broader acceptance of NTC and outlines recent efforts to address these hurdles. [4]. The design and analysis of low power CMOS Static Random Access Memory (SRAM) cells, particularly focusing on 7-transistor (7T) and 9-transistor (9T) configurations, aim to address the challenges of reducing power consumption while maintaining stability and performance in modern integrated circuits. These configurations are explored as alternatives to the conventional 6T SRAM cell to achieve better tradeoffs between power efficiency, read/write stability, and area overhead.7T SRAM Cell: This configuration introduces an additional transistor compared to the standard 6T cell, typically used to enhance read stability or reduce leakage current during standby mode. The extra transistor can act as a read buffer or a sleep transistor to cut off the cell from the bit lines during idle periods, thereby reducing static power consumption [5].

## **III. Low Power 10T SRAM Working**

A low standby power SRAM cell with 10T (LP10T) and high static noise margins is shown in this study. Our suggested design's salient characteristics comprise of A single-ended structure, Utilization of distinct bit lines for read and write functions, Enhanced read stability achieved through Schmitt-trigger and conventional inverters are arranged cross-coupled, and an additional read path is included. Execution of fictitious differential write operations leveraging the write-bit line (WBL) and the WWLA control signal, Enhanced write-ability made possible by writing-assist and pseudo-differential write operations, Reduction of the cell's dormant or escape power usage.

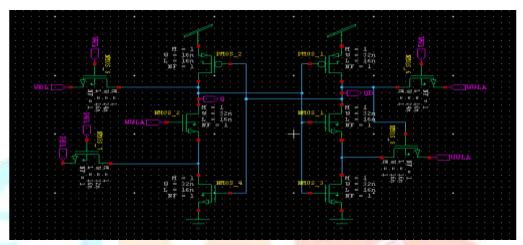

#### LP10TSRAM:

Fig1: Schematic diagram of LP10TSRAM

The suggested LP10T SRAM cell is built upon the cross-coupled architecture of a normal converter with a layered semiconductor (PUL, PDL1, and PDL2) and a pulse trigger-based converter (PUR, PDR1, PDR2, and NF). The cell core stores the information from the actual internal memory clusters Q and QB. Row-based composition word line (WWL) is used to regulate the write accessibility transistors, ACL1 and ACR1. The read accessibility transistor, or ACL2, is gated by the row-based read phrase line (RWL). The column-based command signal (WWLA) governs the read/write support transistor PDL2, which is positioned between the Q and phantom Q (PQ) nodes. Moreover, it is linked to the NF transistor's drain. Separate bit lines, such as column-based RBLas well as WBL for reading and writing, are used in the proposed cell.

#### Truth table:

| Signals | Operations |      |           |           |

|---------|------------|------|-----------|-----------|

|         | Hold       | read | Write '0' | Write '1' |

| RBL     | 1          | E    | 1         | 1         |

| WBL     | 1          | 1    | 0         | 1         |

| RWL     | 0          | 1    | 0         | 0         |

| WWL     | 0          | 0    | 1         | 1         |

| WWLA    | 1          | 1    | 1         | 0         |

#### A. Maintain Position

Both the RWL as well as WWL indicators have been set to '0' during the hold Phase. The storage nodes are decoupled from the bit lines as a result of this operation, which eliminates the access for reading and writing transistors, as shown in Fig 2. The WWLA signals can be switched to '1' in this setup, activating PDL2, guaranteeing that the cell's latch safely preserves the data that has been saved.

## **B.** Bit line with One End Examine the operation

When WWL is decreased to '1', which disables write routes, PDL2 is activated during the read process? As a result, the standard inverter affects the storage node Q. RBL is initially pre-charged to VDD. When RWL is asserted, ACL2 is turned ON, and depending on the number stored at Q, the capacity volt of RBL either drains or stays in its initial elevated pre-charged condition. With the combination of a strong cross-coupled structure with ST and standard inverters, as well as a unique read path, our suggested LP10T SRAM cell solves the read failure problem. Compared to its traditional counterpart, the ST inverter has an exceptionally higher trip voltage. This enhancement stems from the reduction in the strength of PDR2 as Vx increases via the feedback transistor NF. Consequently, as the input voltage to the inverter escalates, the ST inverter demonstrates greater resilience and stability compared to its standard counterpart. In the read '0' operation, the Read Bit Line (RBL) is discharged to GND via a pathway involving the ACL2 and PDL1 transistors. As RBL discharges, the voltage at the PQ node rises from 0 to  $\Delta V$  ( $\Delta V$  equals 0.15 V under extreme Process-Voltage-Temperature (PVT) variations), which subsequently causes an increase in the Q node's voltage through PDL2. This rise ensures that the stored data in the cell remains unchanged, as the voltage does not exceed the trip voltage of the ST inverter. Consequently, the read '0' operation is executed successfully. Thanks to the elimination of the read disturbance issue by our proposed cell, the Read Static Noise Margin (RSNM) matches the Hold Static Noise Margin (HSNM). Nonetheless, when the output voltage of the ST inverter is high (Vout = VDD), the NF transistor activates, leading to a charge in the Vx node. This scenario complicates the alteration of Vout's high value. To address this, we increased the channel length of the PUR transistor in the ST inverter, balancing the '0' and '1' margins.

## C. Write Operation using Pseudo Differential

Changing the Read Word program Line (RWL) indication to '0' to deactivate the read pathway by turning off ACL2 is the first step in starting a write operation. The Write Bit Line (WBL) in our suggested LP10T SRAM cell is driven to '0' to perform the write '0' operation, while WWLA stays at VDD, triggering PDL2. By doing this, a connection is made between the Q node and GND. The write access semiconductors (ACL1 and ACR1) are activated upon the occurrence of the control pulse WWL, enabling the discharge of the stored value of the Q node to the bitline and GND. The QB node is charged concurrently with the activation of the PUR transistor. Furthermore, WWLA makes it easier to write '0' onto the Q node by using the ACR1 transistor to inject '1' onto the QB node. Meanwhile, QB is set to '1', causing the NF transistor to switch on and creating a build-up of charge in the Vx node. The process of writing a '1' into the Q node of the newly developed LP10T SRAM cell involves several steps. Initially, the Write Bit Line (WBL) is raised to VDD. Due to the single-ended design of our proposed cell, inserting a '1' presents a unique challenge. To address this, we introduce an NMOS transistor, labeled PDL2, controlled by WWLA. During the write '1' operation, WWLA is deactivated ('0'), causing PDL2 to cut off. This action severs the connection between GND and the Q node, facilitating the writing of '1'. Subsequently, activating WWL powers up the write access transistors, allowing the value on WBL to be transferred to the Q node. Concurrently, transistors

PDR1 and PDR2 start to activate, leading to the discharge of data stored in node QB to GND. Simultaneously, WWLA assists in writing '1' to the Q node by discharging the QB node via ACR1. With QB set to '0', PUL activates, charging the Q node to VDD. Thus, despite employing a single-ended architecture for the write operation, our design effectively mimics differential operation through strategic use of the WWLA control signal and ACR1 transistor. We observed that the current circuit exhibits higher power consumption, prompting us to develop a novel low-power technology. Let's delve into discussing this innovation.

## **IV. Proposed Method**

In this Chapter, here discussing about the novel design of SRAM using two transistors. The insertion of two transistors represents in above and bottom of the main circuit. Sapon technique is one of the best approach in this low power technologyworld.

## **Introduction to Sapon Technique:**

The SAPON technique is centered on the concept of controlling leakage power, which is a significant contributor to power consumption in VLSI circuits. Leakage power occurs due to the unwanted flow of current through transistors even when they are supposed to be off. To address this issue, SAPON places two leakage-control transistors outside the main logic circuit.

These transistors act as resistors that increase the opposing between the Vdd and Gnd, thereby

controlling the leakage currents.

Fig2: Block diagram of Sapon technique

The SAPON technique is centered on the concept of controlling leakage power, which is a significant contributor to power consumption in VLSI circuits. Leakage power occurs due to the unwanted flow of current through transistors even when they are supposed to be off. To address this issue, SAPON places two leakage-control transistors outside the main logic circuit. These transistors act as resistors that increase the opposing between the Vdd and gnd, thereby controlling the leakage currents.

Here's a more detailed explanation of how the SAPON technique works:

- Transistor Placement: The SAPON transistors are arranged in a stack configuration outside the main logic circuit. This arrangement allows them to provide effective leakage control without being part of the main logic pathway.

- Active Operation: The gate terminals of these SAPON transistors are connected to both the Gnd and

Vdd. This connection ensures that the transistors operate in the active region throughout the operation cycles, which is crucial for their functionas leakage-control devices.

- Lowering Leakage Current: The SAPON transistors lower the beneath the threshold current that leaks during the equilibrium phase and the short contact leakage current throughout the transition phase by raising the opposing connecting Vdd and Gnd. To do this, a greater voltage dip across the transistors is produced, which lowers the current that passes through them.

- Simulation Results: Simulations have shown that the SAPON technique leads to a substantial reduction in power consumption for various logic gates, including inverters, NAND, NOR, and multiplexers. It has been demonstrated to consume 23% less power compared to traditional methods like LECTOR, LCNT, and STACK ONOFIC.

- Area Overhead: Despite its power reduction benefits, the SAPON technique has a comparable area overhead to other leakage control techniques, meaning it does not significantly increase the physical size of the circuit.

The SAPON technique is a viable strategy for creating VLSI designs with minimal power consumption, especially for applications where power efficiency is paramount, such as in battery-operated devices.

### **Introduction to DTMOS Technique:**

The Dynamic Threshold Metal-Oxide-Semiconductor (DTMOS) technique is a methodology applied in the design of semiconductor devices aimed at enhancing performance and decreasing power usage. DTMOS operates by dynamically modifying the Vth of a MOSFET according to the operational circumstances. Such modification is generally accomplished by linking the body (substrate) of the MOSFET to its gate With the transistor switched off, the body effect elevates the threshold voltage, curtailing leakage currents and conserving energy. Conversely, when activated, the threshold voltage diminishes, boosting the drive current and optimizing performance.

Fig3: Block diagram of DTMOS technique

Advantages of DTMOS

1. Energy Efficiency:

Decreased leakage currents in the off position contribute to diminished static power usage.

2. Boosted Performance:

Reduction in threshold voltage during activation facilitates quicker switching times and superior functionality.

3. Flexibility:

DTMOS adapts threshold voltage for varying power and performance needs

#### In SRAM Cells:

Within Static Random-Access Memory (SRAM) cells, DTMOS aids in attaining lower power utilization without sacrificing read/write capabilities. Body Bias Regulation, Accurate regulation of the body bias necessitates meticulous engineering to guarantee the advantages of DTMOS are leveraged without introducing reliability concerns. The DTMOS approach represents a sophisticated strategy for curbing power usage and augmenting performance in contemporary electronics. Through dynamic modulation of the threshold voltage in MOSFETs, DTMOS facilitates proficient energy management, proving invaluable in scenarios demanding a harmony between power conservation and peak performance.

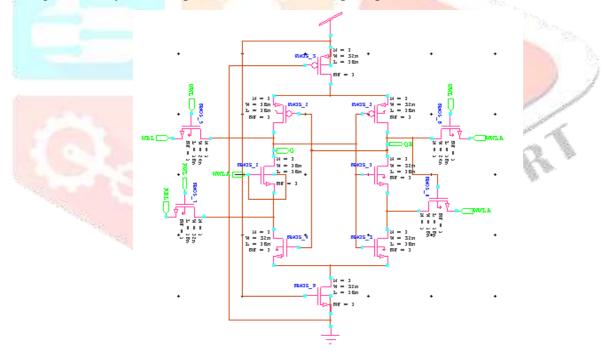

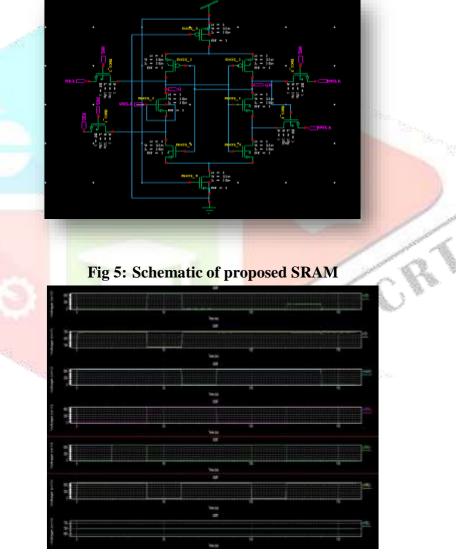

Fig4: Schematic of proposed SRAM using Sapon Technique & DTMOS Technique

#### **V. RESULT AND ANALYSIS**

The Results and Discussion portion offers a thorough assessment of the Proposed SRAM architecture, utilizing S-edit within Tanner EDA. Prior to proceeding with simulations, the design phase meticulously verified the schematic and connections for accuracy. Simulations were conducted through T-Spice, encompassing essential procedures such as integrating a technology file, setting the simulation duration, identifying input sources, and adding directives for computing power usage and latency. Initiation of the simulation was accomplished by selecting "run simulation." After the simulation concluded, a detailed inspection of the waveforms was undertaken to evaluate the Proposed SRAM structure's performance across different

scenarios. This scrutiny extended to a comprehensive review of MOSFET operation, power consumption levels, and delay times. Insights gleaned from the waveform analysis shed light on the dynamic characteristics of the proposed design, facilitating an in-depth evaluation of its operational efficiency and performance indicators. Analyzing MOSFET usage provided significant understanding regarding the efficiency and resource allocation within the engineered Flip-Flop (FF) structure. It was necessary to closely examine electrical usage levels in order to evaluate the suggested design's conservation of energy. In order to comprehend the adaptability and operating speed of the suggested 10T SRAM arrangement, delay factors were also examined.

The Results and Discussion segment provides an exhaustive examination of the suggested SRAM configuration., integrating simulation outcomes with insightful discussions to provide a holistic understanding of the design's performance and potential areas for improvement.

Fig 6: Simulation Waveforms

## **COMPARISION TABLE:**

|          | Area | Power                    | Delay                     |

|----------|------|--------------------------|---------------------------|

| Existing | 10   | 5.125 x 10 <sup>-8</sup> | 2.00 x 10 <sup>-8</sup>   |

| Proposed | 12   | 3.858 x 10 <sup>-8</sup> | 1.503 x 10 <sup>-10</sup> |

In existing method we design the 10T SRAM with access transistors, for strengthening the signal we add 2 transistors. While design the existing method the Power values is  $5.125 \times 10^{\circ}$ -8 while we try to reduce the power, we use the low power technique as "Sapon approach and DTMOS technique". Using Sapon approach and DTMOS technique we have observed that Power got decreased trading area with constant delay.

#### VI. CONCLUSION

This study presents an enhanced SRAM cell design incorporating an extra sleep transistor, aimed at achieving reduced power consumption and increased stability. Our approach integrates both Sapon methodology and DTMOS technology within the traditional 10T SRAM circuit structure. Comparing the outcomes makes it evident that the suggested strategy offers lesser power consumption than the conventional SRAM circuit observing from simulated results obtained by Tanner EDA.

#### **REFERENCES**

- [1] D. P. Madelo, A. Tayros, R. Sabarillo, A. Lowaton and J. Hora, "Design of Low Power P-Gated Schmitt Trigger SRAM in 65nm CMOS Technology," 2018 International Conference on Control, Electronics, Renewable Energy and Communications (ICCEREC), Bandung, Indonesia, 2018, pp. 189-194, doi: 10.1109/ICCEREC.2018.8711999.

- [2] S. K. K, K. P. B, V. M and R. K. R. D V, "A Design of Low Power Full Seu Tolerance RHBD 10t Sram Cell," 2020 IEEE India Council International Subsections Conference (INDISCON), Visakhapatnam, India, 2020, pp. 27-32, doi: 10.1109/INDISCON50162.2020.00018.

- [3] E. Abbasian, F. Izadinasab and M. Gholipour, "A Reliable Low Standby Power 10T SRAM Cell With Expanded Static Noise Margins," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 69, no. 4, pp. 1606-1616, April 2022, doi: 10.1109/TCSI.2021.3138849.

- [4] E. Abbasian, F. Izadinasab and M. Gholipour, "A Reliable Low Standby Power 10T SRAM Cell With Expanded Static Noise Margins," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 69, no. 4, pp. 1606-1616, April 2022, doi: 10.1109/TCSI.2021.3138849.

- [5] Design and Analysis of Low Power CMOS SRAM Cells 7T and 9T, April 2022 DOI:10.1109/ICETET-SIP- 2254415.2022.9791506 Conference: 2022 10th International Conference on Emerging Trends in Engineering and Technology - Signal and Information Processing (ICETET-SIP-22

- [6] M. Maymandi-Nejad and M. Sachdev, "DTMOS Technique for Low-Voltage Analog Circuits," in IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, vol. 14, no. 10, pp. 1151-1156, Oct. 2006, doi: 10.1109/TVLSI.2006.884174.

- [7] B. Calhoun and A. Chandrakasan, "Static noise margin variation for sub-threshold SRAM in 65-nm CMOS," IEEE J. Solid-State Circuits, vol. 41, no. 7, pp. 1673–1679, Jul. 2006.

- [8] R. G. Dreslinski, M. Wieckowski, D. Blaauw, D. Sylvester, and T. Mudge, "Near-threshold computing: Reclaiming Moore's law through energy efficient integrated circuits," Proc. IEEE, vol. 98, no. 2, pp. 253–266, Feb. 2010

- [9] B. H. Calhoun, J. F. Ryan, S. Khanna, M. Putic, and J. Lach, "Flexible circuits and architectures for ultralow power," Proc.IEEE, vol. 98, no. 2, pp. 267–282, Feb. 2010.

- [10] R. Baumann, "Radiation-induced soft errors in advanced semiconductor technologies," IEEE Trans. Device Mater. Rel., vol. 5, no. 3, pp. 305–316, Sep. 2005.

- [11] M.-H. Chang, Y.-T. Chiu, and W. Hwang, "Design and iso-area Vmin analysis of 9T subthreshold SRAM with bit-interleaving scheme in 65-nm CMOS," IEEE Trans. Circuits Syst., II, Exp. Briefs, vol. 59, no. 7, pp. 429–433, Jul. 2012.

- [12] P. Hazucha et al., "Neutron soft error rate measurements in a 90-nm CMOS process and scaling trends in SRAM from 0.25-mm to 90-nm generation," in IEDM Tech. Dig., Dec. 2003, pp. 21.5.1–21.5.4.

- [13] I. J. Chang, J.-J. Kim, S. P. Park, and K. Roy, "A 32 kb 10T sub threshold SRAM cell array with bit-interleaving and differential read scheme in 90 nm CMOS," IEEE J. Solid-State Circuits, vol. 44, no. 2, pp. 650–658, Feb. 2009.

- [14] L. Chang et al., "An 8T-SRAM for variability tolerance and low-voltage operation in high-performance caches," IEEE J.Solid-State Circuits, vol. 43, no. 4, pp. 956–963, Apr. 2008.

- [15] G. Pasandi and S. M. Fakhraie, "A 256-kb 9T near-threshold SRAM with 1k cells per bitline and enhanced write and read operations," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 11, pp. 2438–2446, Nov. 2015

- [16] J. Kulkarni, K. Kim, and K. Roy, "A 160 mV robust Schmitt trigger based sub-threshold SRAM cell," IEEE J. Solid-State Circuits, vol. 42, no. 10, pp. 2303–2313, Oct. 2007.

- [17] S. Ahmad, M. K. Gupta, N. Alam, and M. Hasan, "Single-ended Schmitt-trigger-based robust low-power SRAM cell," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 24, no. 8, pp. 2634–2642, Aug. 2016.

- [18] Y. Xie, Emerging Memory Technologies: Design, Architecture, and Applications. Springer, Oct. 2013, p. 187.

- [19] M.-H. Tu et al., "A single-ended disturb-free 9t subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing," IEEE J. Solid-State Circuits, vol. 47, no. 6, pp. 1469–1482, Jun. 2012.

- [20] T. W. Oh, H. Jeong, K. Kang, J. Park, Y. Yang, and S.-O. Jung, "Power-gated 9T SRAM cell for low-energy operation," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 25, no. 3, pp. 1183– 1187, Mar. 2017.

- [21] BSIM-CMG 107.0.0 Multi-Gate MOSFET Compact Model. Accessed: Jul. 2013. [Online]. Available:http://www.device.eecs.berkeley.edu/bsim/?page=BSIMCMG\_LR

- [22] C. Auth et al., "A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," in Proc. Symp. VLSI Technol., Jun. 2012, pp. 131–132.

- [23] C.-H. Lin et al., "Channel doping impact on FinFETs for 22 nm and beyond," in Proc. Symp. VLSI Technol., Jun. 2012, pp. 15–16.

- [24] Z. Guo, A. Carlson, L.-T. Pang, K. T. Duong, T.-J.-K. Liu, and B. Nikolic, "Large-scale SRAM variability characterization in 45 nm CMOS," IEEE J. Solid-State Circuits, vol. 44, no. 11, pp. 3174–3192, Nov. 2009.

- [25] J. Wang, S. Nalam, and B. H. Calhoun, "Analyzing static and dynamic write margin for nanometer SRAMs," in Proc. 13thInt. Symp. Low Power Electron. Design (ISLPED), 2008, pp. 129–134.