ISSN: 2320-2882

# INTERNATIONAL JOURNAL OF CREATIVE **RESEARCH THOUGHTS (IJCRT)**

An International Open Access, Peer-reviewed, Refereed Journal

# **Multi-Level SMES-Based DVR for Improving** Voltage Quality in Primary Distribution Network

Gunturu Anand<sup>1</sup>, P.S.D. Bhima Raju<sup>2</sup>, Ch. Amarendra<sup>2</sup> <sup>1</sup>P.G. Scholar, <sup>2</sup>Associate Professor Department of Electrical and Electronics Engineering

<sup>1,2</sup>Aditya Engineering College(A), Surampalem, Andhra Pradesh, India

Abstract: A dynamic voltage restorer (DVR), intended to protect customers from voltage changes, is one of the modern power electronic controllers in the distribution system. The distribution system's voltage signal is organized by DVR output compensating signals. To increase voltage quality, this study introduces SFCL's fault current limiter and SMES's integrated DVR. The performance of the SMES integrated DVR for improving voltage quality is considered to be presented during voltage sag conditions. Furthermore, because of the additional voltage enhancement offered by SFCL, the power that DVR injects into the load is reduced. Utilizing MATLAB/Simulink, the simulation model and outcomes are analyzed.

Index Terms - Dynamic voltage restorer (DVR), Voltage quality

#### I. Introduction

Voltage variations and short-circuit failures are the two main issues that modern power systems must handle [1], [8]. The grid has generators that use renewable energy sources (such as wind and solar) and can provide a range of outputs. Additionally, the popularity of distributed generation and the exponentially rising demand for power have raised fault current levels.

To reduce voltage fluctuations, a dynamic voltage restorer (DVR) may produce a compensation voltage that is introduced into the grid via a series transformer [12]-[16]. However, when there is a fault, a significant short-circuit current will be introduced into the VSI via a transformer. An alternative for this issue is a bypass strategy. The DVR can be taken down as a "fail-safe" system [6]. Enhancing DVR effectiveness is a different strategy [20]. The series compensator can perform load-side voltage restoration for upstream faults and current restriction for downstream faults thanks to the control techniques depicted in [20]. This method's drawback is that a sizable storage system is required on the dc side. The proposed method also includes a varistor and a few antiparallel thyristors that are connected in parallel to the series transformer's secondary winding [6]. The main method of protection is a varistor, and it is challenging to produce the low-saturation magnetic properties of the series transformer. Nevertheless, the architecture simply shields the series VSI from the excess current and does not prohibit big currents from flowing

The topologies of fault current limiters (SFCLs), superconducting magnetic energy storage (SMES), solid-state SFCLs, and resonance-type SFCLs, on the other hand, differ [19], [13]. The extra equipment will, however, necessarily increase the total investment and capital cost. Therefore, it would be preferable to enhance the DVR's current capabilities to also reduce the shortcircuit current. By including a new branch, the series compensator might accomplish various functions [5], [11]. A thyristorswitched inductor branch in the proposed DVR also allows for power factor adjustment [5]. Additionally, a typical method involves connecting the bypass in parallel to the primary of the series transformer [11]. The apparatus comprises a mechanical bypass switch that enables bypassing of the static series compensator (SSC) and a bypass electronic switch composed of two parallel thyristors [4]. The fault current is not constrained to the desired value even though the SSC is protected during faults. Superconducting magnetic energy storage (SMES) was suggested as a fault current-limiting dynamic voltage restorer (SFCL-DVR) in [21]. The SFCL-transient DVR's condition, however, was not fully characterized. The current-limiting module's thermal stability and maximum withstand voltage were also disregarded. The series transformer ratio's ideal parameter selection has not been considered [21]. In contrast, a high-power multilayer inverter generates less harmonic current and necessitates power switches with lower ratings [3]-[10]. The design and use of the multifunctional system depend greatly on the aforementioned characteristics.

To lower the transformer's ratio, a brand-new multilayer Diode Clamped dynamic voltage restorer (MD-DVR) is presented in this work. Similar cascade inverter performance advantages, such as lower power ratings and cheaper power devices, are offered by the MD-DVR. Additionally, it immediately restricts the short-circuit current during failures and provides the system with more effective protection.

# II. The Principle and Control Strategy of SMES DVR 1 Principle

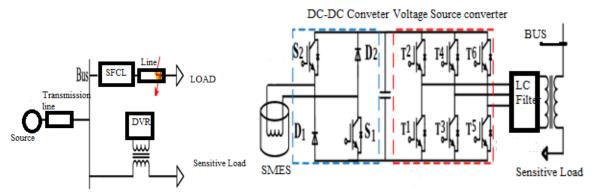

Fig.1. (a) block diagram for the proposed system

Fig.1. (b) SMES-based DVR.

Figure 1a shows the SMES-based DVR and SFCL circuit architecture. Figure 1 depicts the major components of the sensitive load side SMES-based DVR: a VSC, in-grid transformer, DC-link capacitor, and SMES device formed from a single SMES magnet and Chopper. (b). SFCL connects the feeds in series.SMES and SFCL reduce voltage sag for sensitive loads. If a 3-φ fault appears in a line without a sensitive load, the fault current and bus voltage will be limited. As soon as a voltage sag is noticed, the SMES-based DVR corrects the voltage of the sensitive load.

#### 2. SMES-DVR Management Technique

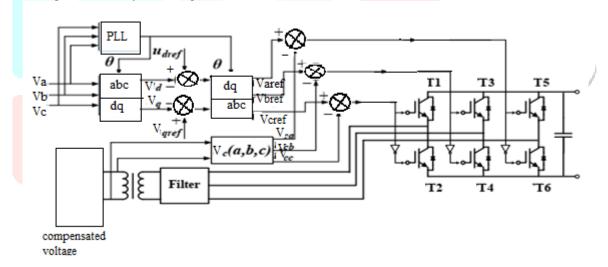

Figure 2 depicts the control approach for the SMES-based DVR, which includes controlling the DC-DC converter and the VSC. The DC-DC converter uses the DC voltage control method to keep the DC voltage constant. The difference between the dc voltage reference and the actual value is passed to a hysteresis buffer to generate a PWM control signal to operate the two switches (S1, S2). The dc voltage can be regulated by manipulating the on-off state of two switches to achieve a repeat transition between charge mode (S1 ON, S2 ON) and discharge mode (S1 OFF, S2 OFF) for SMES. It is crucial to stress that the SMES cannot be guaranteed to operate normally if the magnet current is excessive.

Figure. 2. The VSC presag compensation plan.

Additionally, as illustrated in Fig., a pre-sag compensation technique with dq transform is used to manage the VSC [11]. To accurately correct voltage quality disturbances caused by instantaneous reactive power theory and hysteretic voltage management method, The sensitive load voltage's real-time magnitude, and phase angle are individually locked and saved. The pre-sag strategy produces the least amount of transient voltage waveform distortion when compared to other approaches such as phase or optimized-energy compensation.

#### 3 Equivalent Resistance Modelling of SFCL

The resistance feature of the SFCL has been studied in our earlier work [7], [15], which suggests that the SFCL will behave differently in terms of its physical state and resistance features depending on the current passing through it. Additionally, under various operating situations, the SFCL resistance value is separated into 5 operational sectors.

$$Rsf = \begin{cases} 0 & t < ts \\ SE_{c}I_{r}^{n-1}/I_{c}^{n} & ts < t < te \\ Rm & t_{1} < t < t_{1} \\ R_{m}e^{-(t-t_{e})/t_{2}} & te < t < t_{2} \\ 0 & t > t_{2} \end{cases}$$

(1)

## **III. Estimation of SMES and SFCL Parameters**

## **Design of SMES Magnet**

A high critical current is required when using the SMES magnet with a resistive SFCL device because of the necessity for the short-term, high-power energy exchange. [21] An inductance of 1.5 H and 800 A critical current are employed in this research [21]. The SMES magnet has a set of nine pancake assemblies at each end. The central assembly consists of ten parallel pancakes, each with fifty coil turns. It measures 270 millimeters across the top and 240 millimeters across the bottom. Four symmetrical assemblies on each side, with 5 serial pancakes from each coil end to the centerpiece, are used to generate a step-shaped cross-sectional shape. Two-inch, two-inch, and two-and-a-half-inch inner diameters are available. To meet the extended standards of the SMES, four step-shaped components are coupled parallel in series. The total tape length for this SMES magnet is around 20 kilometers. B. Estimation of SFCL's Resistance

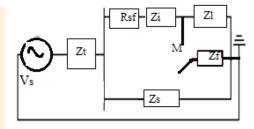

Equivalent circuit diagrams for the distribution system shown in Figure 1(a) are illustrated in Figure 4. Faults in one line cause the switch K to be closed and bus voltage to be stated in terms of volts.

$$Vbus = \frac{Zi}{Z_t(Z_i + Z_s) + Z_i Z_s} V_s$$

(2)

Where,

$$Z_{l} = R_{m} + Z_{i} + \frac{Z_{l} + Z_{f}}{Z_{l}Z_{f}}$$

(3)

Total transmission line impedance (Zt) is equal to the sum of the load impedance and the equivalent line impedance (Zi), and sensitive load impedance (Zs) is equal to the impedance of the sensitive load.

The bus voltage (Vbus) is dependent on the SFCL resistance Rm, according to equation (2). Accordingly, it is possible to estimate the SFCL resistance to meet the required bus voltage requirement (2).

Fig. 4. Block diagram of distribution system equivalent circuit.

#### II. 5-LEVEL DIODE CLAMPED INVERTER

Basic bridge inverters have been modified to produce multi-level devices. The most common configuration is to link them in series to create level stacks.

The multilevel inverter's topological structure must address the following issues:

- 1. To the extent practical, it should contain fewer switching devices.

- 2. It should be able to withstand very high input voltages, such as those used in high-voltage direct current (HVDC) transmission. Due to the multi-level strategy, each switching device should have a reduced switching frequency.

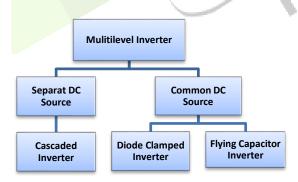

# 1. Types of Multilevel Inverters

Figure 5 Multilevel Inverter types

### Diode Clamped Multi-Level Inverter

Recent years have seen an increase in the number of industrial uses calling for greater power equipment. Megawatt power levels are required in several medium voltage motor drives and utility applications. Only one power semiconductor switch may be directly connected to a medium voltage grid without causing issues. As a consequence, in circumstances requiring high power and medium voltage, a multilayer power converter structure has been proposed. In addition to achieving large power ratings, a multilayer converter also makes it possible to utilize renewable energy sources. It is simple to connect high-power renewable energy sources like photovoltaics, wind turbines, and fuel cells to converter systems with many levels of output regulation. NABE-EL has brought the idea of multi-level converters to the industry. Low distortion and lower dv/dt, low input current distortion, reduced common-mode (cm) voltage, and lower switching frequency are some of the advantages of using MOSFETs in the 1970s and early 1980s. There are several benefits to using multi-level inverters. The diode clamped multilevel inverter also went by the name of the "neutral point clamped" (NPC) inverter. To effectively double device voltage levels without requiring precise voltage matching, a three-level NPC inverter was used for the first time.

#### **Advantages**

The harmonic content will be so low as to obviate the need for filters if there are enough levels. A great degree of efficiency is achieved by using a single fundamental frequency to switch all devices. Controlling the flow of reactive power is possible. A back-to-back intertie system has a simple control mechanism.

DCMI may be used as a multiplexer to link an output to one of the available nodes. However, despite their lower current, primary diodes are authorized to operate at the same voltage as the main power devices. DCMI capacitors are only required to filter out low-order components as they naturally cancel each other out. Only a capacitor's voltage is impeded in each power supply. Clamping diodes are used to protect electronic equipment from the damaging effects of a reverse current.

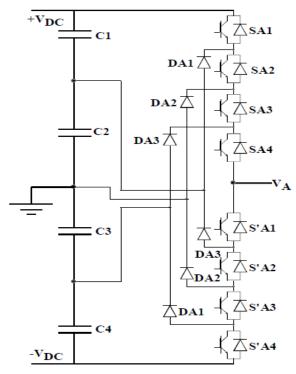

Figure 6 Schematic diagram of Diode Clamped Multi-Level Inverter

| Table 1 Switching Sequence For 3 Lever |    |    |    |    |     |     |     |     |  |

|----------------------------------------|----|----|----|----|-----|-----|-----|-----|--|

| output                                 | s1 | s2 | s3 | s4 | s1' | s2' | s3' | s4' |  |

| $3V_{dc}/4$                            | 0  | 1  | 1  | 1  | 1   | 0   | 0   | 0   |  |

| 0                                      | 0  | 0  | 0  | 0  | 1   | 1   | 1   | 1   |  |

| $V_{dc}/4$                             | 0  | 0  | 0  | 1  | 1   | 1   | 1   | 0   |  |

| $V_{dc}/2$                             | 0  | 0  | 1  | 1  | 1   | 1   | 0   | 0   |  |

| 0                                      | 0  | 0  | 0  | 0  | 1   | 1   | 1   | 1   |  |

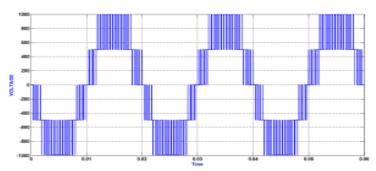

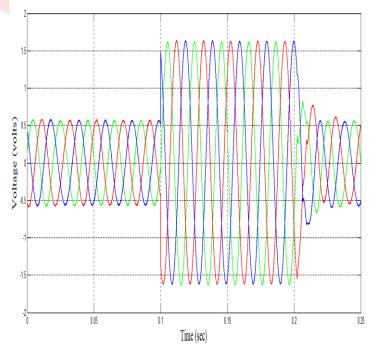

Figure 7 Output waveform of Diode Clamped Five level Inverter

# III. SIMULATION RESULTS:

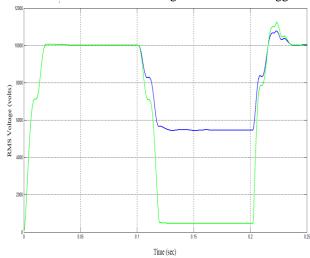

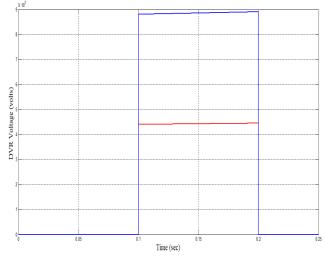

Time (sec) 8. (a) distribution line 1 fault current with a single DVR and the suggested SFCL&DVR.

8. (b) The suggested SFCL&DVR and the common bus RMS voltage with a single DVR.

The distribution line 1 fault current is shown in Fig. 8 along with two voltage compensation techniques. The first peak value of the fault current is reduced and is lower with the suggested cooperative strategy integrating SFCL and DVR (SFCL&DVR) than it is with the solo DVR scheme.

Fig.9. The suggested SFCL&DVR and a single DVR's output compensated for the power of the DVR.

Figure 9 displays the output corrected power of the DVR using two compensation strategies. The output compensated power of the DVR is decreased by the suggested SFCL&DVR method to 0.54 MW, which is 1.63 times less than that of the single DVR design (0.88 MW). This is a result of the additional SFCL's ability to reduce common bus voltage sag depth through its voltageenhancement effect, hence reducing the adjusted power demand DVR and capital

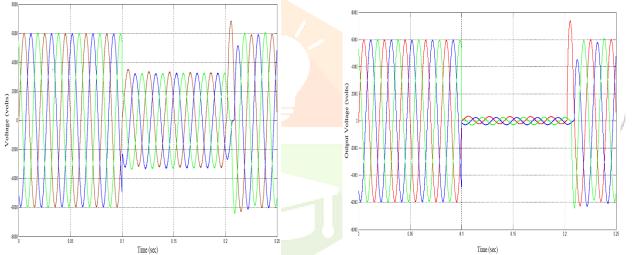

Fig. 10. (a) The sensitive load voltage without compensation.

Fig. 10. (b). The DVR output voltage with a single DVR.

Fig. 10. (c). The DVR output voltage with proposed SFCL&DVR.

Fig.10.(d). The sensitive load voltage with compensation.

Fig. displays the terminal voltage of the delicate load and the DVR output voltage with various voltage compensation strategies. 10. Comparing Fig. combined with Fig. In Figure 10(d), it is clear that both the single DVR and the suggested SFCL&DVR scheme are capable of fully increasing the sensitive load voltage to pre-fault value in under 8 milliseconds, essentially removing the negative effects of voltage sag on sensitive loads.

Additionally, the proposed SFCL&DVR strategy will boost the DVR output voltage compared to the single DVR scheme due to the additional voltage enhancement of the common bus via SFCL.

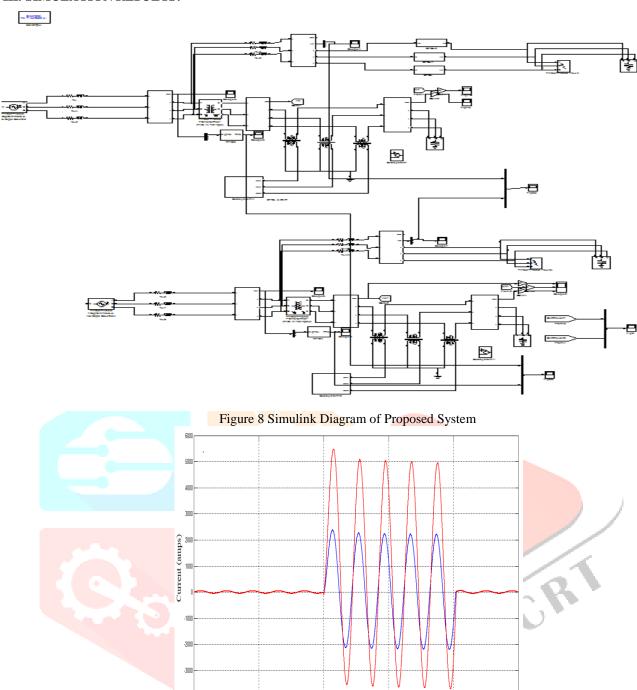

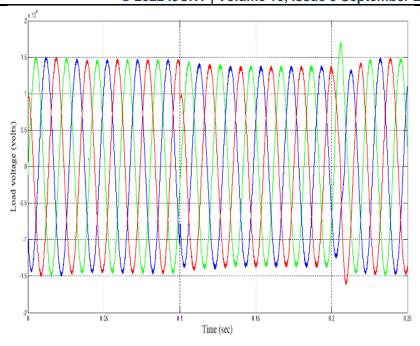

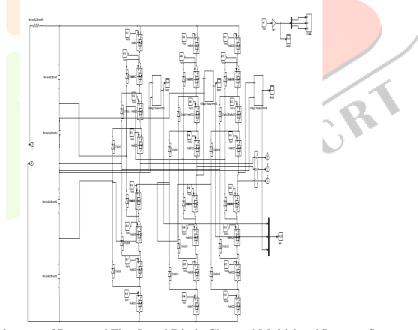

Figure 12 Simulink Diagram of Proposed Five Level Diode Clamped Multi-level Inverter System

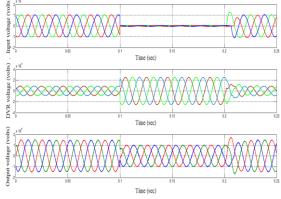

Fig.12. Simulation waveforms of Proposed Five Level Diode Clamped Multi-level Inverter System (a) Input Voltage (b) DVR Voltage (c) Output Voltage

#### IV. CONCLUSION

SMES-based DVR system coupled with SFCL has been suggested and tested to compensate for voltage sags. This paper presents and discusses in depth the conceptual design as well as the compensation principle, control technique, parameter assessment, simulation results, and performance evaluationSMES-based DVR system with pre-sag compensation may be able to retain the sensitive load voltage at its pre-fault value as long as the common bus fails. The additional SFCL's high resistance does more than only aid in the reduction of fault current. A further benefit of this approach is that it reduces DVR's total capital expenditures by reducing DVR's voltage-enhancement impact on a single common bus to a minimum. An MW-class SMES-based DVR system with SFCL may improve transient voltage quality in a modern distribution power system.

#### REFERENCES

- [1] X. H. Jiang et al., "A 150 kVA/0.3 MJ SMES voltage sag compensation system," IEEE Trans. Appl. Supercond., vol. 15, no. 2, pp. 1903–1906, Jun. 2005.

- [2] S. Suzuki, J. Baba, K. Shutoh and E. Masada, "Effective application of superconducting magnetic energy storage (SMES) to load leveling for high-speed transportation system," IEEE Trans. Appl. Supercond., vol. 14, no. 2, pp. 713-716, June 2004.

- [3] J. F. Moon, S. H. Lim, J. C. Kim and S. Y. Yun, "Assessment of the Impact of SFCL on Voltage Sags in Power Distribution System," IEEE Trans. Appl. Supercond., vol. 21, no. 3, pp. 2161-2164, June 2011.

- [4] L. Ye, M. Majoros, T. Coombs and A. M. Campbell, "System Studies of the Superconducting Fault Current Limiter in Electrical Distribution Grids," IEEE Trans. Appl. Supercond., vol. 17, no. 2, pp. 2339-2342, June 2007.

- [5] Z. X. Zheng, X. Y. Chen, X. Y. Xiao and C. J. Huang, "Design and Evaluation of a Mini-Size SMES Magnet for Hybrid Energy Storage Application in a kW-Class Dynamic Voltage Restorer," IEEE Trans. Appl. Supercond., vol. 27, no. 7, Oct. 2017, Art. no.

- [6] M. A. Green and B. P. Strauss, "The Cost of Superconducting Magnets as a Function of Stored Energy and Design Magnetic Induction Times the Field Volume," IEEE Trans. Appl. Supercond., vol. 18, no. 2, pp. 248-251, June 2008.

- [7] Z. C. Zou, X. Y. Chen, C. S. Li, X. Y. Xiao and Y. Zhang, "Conceptual Design and Evaluation of a Resistive-Type SFCL for Efficient Fault Ride Through in a DFIG," IEEE Trans. Appl. Supercond., vol. 26, no. 1, Jan. 2016, Art. no. 5600209.

- [8] S.Nagaya et al., "Field test results of the 5MVASMESsystem for bridging instantaneous voltage dips," IEEE Trans. Appl. Supercond., vol. 16, no. 2, pp. 632–635, Jun. 2006.

- [9] X. Y. Chen, and J. X. Jin, "Evaluation of step-shaped solenoidal coils for current-enhanced SMES application," IEEE Trans. Appl. Supercond., vol. 24, no. 5, Oct. 2014, Art. no. 4603404.

- [10] J. S. Kim, S. H. Lim, J. C. Kim and J. F. Moon, "A Study on Bus Voltage Sag Considering the Impedance of SFCL and Fault Conditions in Power Distribution Systems," IEEE Trans. Appl. Supercond., vol. 23, no. 3, pp. 5601604-5601604, June 2013.

- [11] Z. Zheng, X. Xiao, X. Chen, C. Huang, L. Zhao and C. Li, "Performance Evaluation of a MW-Class SMES-BES DVR System for Mitigation of Voltage Quality Disturbances," IEEE Trans. Ind. Appl., vol. 54, no. 4, pp. 3090-3099, July-Aug. 2018.

- [12] W. Y. Guo et al., "Control strategy of a 0.5 MVA/1 MJ SMES based dynamic voltage restorer," IEEE Trans. Appl. Supercond., vol. 20, no. 3, pp. 1329-1333, Jun. 2010.

- [13] Z. X. Zheng, X. Y. Xiao, C. S. Li, Z. Chen and Y. Zhang, "Performance Evaluation of SMES System for Initial and Steady Voltage Sag Compensations," IEEE Trans. Appl. Supercond., vol. 26, no. 7, pp. 1-5, Oct. 2016, Art. no. 5701105.

- [14] K. Shikimachi et al., "Development of MVA class HTS SMES system for bridging instantaneous voltage dips," IEEE Trans. Appl. Supercond., vol. 15, no. 2, pp. 1931–1934, Jun. 2005.

- [15] Z. C. Zou, X. Y. Xiao, Y. F. Liu, Y. Zhang and Y. H. Wang, "Integrated protection of DFIG-based wind turbine with a resistivetype SFCL under symmetrical and asymmetrical faults," IEEE Trans. Appl. Supercond., vol. 26, no. 7, Oct. 2016, Art. no. 5603005.

- [16] J. H. Zhu et al., "Design, dynamic simulation and construction of a hybrid HTS SMES (high-temperature superconducting magnetic energy storage systems) for Chinese power grid," Energy, vol. 51, no. 2, pp. 184–192, Mar. 2013.

- [17] J. F. Moon and J. S. Kim, "Voltage Sag Analysis in Loop Power Distribution System With SFCL," IEEE Trans. Appl. Supercond., vol. 23, no. 3, pp. 5601504-5601504, June 2013.

- [18] K. Shikimachi et al., "System coordination of 2 GJ class YBCO SMES for power system control," IEEE Trans. Appl. Supercond., vol. 19, no. 3, pp. 2012-2018, Jun. 2009.

- [19] J. W. Shim, Y. Cho, S. J. Kim, S. W. Min and K. Hur, "Synergistic Control of SMES and Battery Energy Storage for Enabling Dispatchability of Renewable Energy Sources," IEEE Trans. Appl. Supercond., vol. 23, no. 3, pp. 5701205-5701205, June 2013.

- [20] L. Y. Xiao et al., "Fabrication and tests of a 1 MJ HTS magnet for SMES," IEEE Trans. Appl. Supercond., vol. 18, no. 2, pp. 770-773, Jun. 2008.

- [19] J. W. Shim, Y. Cho, S. J. Kim, S. W. Min and K. Hur, "Synergistic Control of SMES and Battery Energy Storage for Enabling Dispatchability of Renewable Energy Sources," IEEE Trans. Appl. Supercond., vol. 23, no. 3, pp. 5701205-5701205, June 2013.

- [21] M. Jafari, S. B. Naderi, M. T. Hagh, M. Abapour and S. H. Hosseini, "Voltage Sag Compensation of Point of Common Coupling (PCC) Using Fault Current Limiter," IEEE Trans. Appl. Supercond., vol. 26, no. 4, pp. 2638-2646, Oct. 2011.

- [22] Z. Zheng, X. Xiao, C. Huang and C. Li, "Enhancing Transient Voltage Quality in a Distribution Power System With SMES-Based DVR and SFCL," in IEEE Transactions on Applied Superconductivity, vol. 29, no. 2, pp. 1-5, March 2019, Art no. 5400405, doi: 10.1109/TASC.2018.2882469.