IJCRT.ORG

ISSN: 2320-2882

# INTERNATIONAL JOURNAL OF CREATIVE RESEARCH THOUGHTS (IJCRT)

An International Open Access, Peer-reviewed, Refereed Journal

# A NEWLY MODIFIED SEVEN LEVEL **CASCADED H BRIDGE INVERTER WITH** REDUCED COMPONENTS

<sup>1</sup>Sandhyaranireddy, <sup>2</sup>Chandrasekhara Seregara

Department of Electrical and Electronics Engineering

Poojya Doddappa Appa College of Engineering, Kalaburagi, Karnataka, India

there gate drives compared with the existing cascaded multi level inverter

**ABSTRACT**: A multilevel inverter is used in power conversion methodology for, high power applications and high voltage in today's power grid's, transportation systems, transmission system and industrial motor drives etc.

A seven level modified cascaded H bridge inverter is suggested to Reduced number of switching elements, such that the number of driver circuits requiring low dv / dt stress on each switch is also reduced, switching losses also decreased. A seven-level modified cascaded H bridge inverter is simulated and produces the same output voltage of 7 stages, the suggested multilevel inverter needs only 6 switches where 8 switches are needed as the traditional form. This topology can eliminate roughly half the number of switches,

## I. INTRODUCTION

Due to growing numbers of customers as well as high power industries, the power grid has experienced high energy demand over the last decade. Due to the advancement of semiconductor equipment technology, electronic control equipment replaces traditional bulky transformers significantly. In renewable energy conversion systems , power inverters are commonly used to provide green power to customers. The economic cost of power switches makes them efficient and allows them to succeed in the market. The use of more switches in the inverter structure does not dramatically increase the price, so two-tier traditional converters with high power losses and harmonic content are quickly replaced by low switching frequency multi-level inverters. Many studies have concentrated on the development of multilevel inverters, both in topology and control strategy aspects. The main focus is on the number of components used in these forms of inverters.

The inverter is used for emergency backup power at industrial and domestic applications. The AC power is used mainly for electrical device like lights, motor, and other devices. The voltage source inverter produces an output voltage levels 0, +VDC or -VDC. They A newly modified seven level cascaded H-bridge inverter focus on modeling and simulation of single phase inverter as a frequency changer by PWM. The model is implemented using MATLAB/SIMULINK software. The operation procedure of the inverter is detailed and is demonstrated with SIMULINK. Hence suggested model provides improved performance or more effective with less switching loss and total harmonic distortion. The simulation is carried out in MATLAB2013b, for a seven level modified cascaded H bridge inverter is developed in MATLAB/SIMULIN

Keywords: Inverter, multilevel inverter, cascaded H-bridge, modified cascaded H-bridge.

are known as two-level inverter. To obtain a quality output voltage or current waveform with a minimum amount of ripple content, they required high switching frequency along with various pulse width modulation techniques. In high power and high voltage application, these two level inverter have some limitations in operating at high frequency mainly

energy resources need power electronics inverters as interface to deliver power to the grid and loads. Reducing the environmental pollution by increasing the efficiency due to switching, conduction losses and constraints of device ratings. Therefore, multilevel inverters have been introduced.

A multi level inverter is a power electronic circuit which is capable of providing desired alternating voltage level at the output using multiple lower level DC voltages as an input. In the last few years there is growing interest in multilevel topologies, because of many possibilities of expanding areas of power electronics use. It can also extend the application of power converters to higher voltage and power ratio.

A Multilevel Inverter Cascaded H-Bridge is a sequence of multiple H-bridge inverter links. Each inverter for the H-bridge has the same configuration as a standard full-bridge single-phase inverter. The concept of using different DC sources to generate an AC voltage waveform is introduced by the cascaded H-bridge multilevel inverter. Each inverter with an H-bridge is linked to its own VDC DC source. An AC voltage waveform is produced at the output by cascading the AC outputs of each H-bridge inverter. Each H-bridge inverter can produce three different voltages, namely + VDC, 0 and

-VDC, by selecting the necessary switches.

The 7-level cascaded H-bridge multilevel inverter the simulations will be carried out for different levels like 3- level, 5-level, 7-leve and the output waveforms for these

1

levels will be shown. The simulation results will be carried out.

To overcome the problems associated with single phase full bridge inverter like high total harmonic distortion, high electromagnetic interference, low quality output voltage waveform, high conduction and switching losses, software is going to be developed for "cascaded H-bridge seven level inverter with reduced switch count" to obtain 7 different levels of output voltage (i.e. 36V, 24V, 12V, 0, -12V, 24V, -36Vapproximately) with two separate DC sources

#### II. RELATED WORK

A redesigned cascaded seven-level H-bridge inverter has the benefit of decreased total harmonic distortion, portability, and cost compared with the conventional cascaded H bridge inverter. This paper presents the working of a system of LC philtre that allows to get closer to the sinusoidal waveform. This topology requires a smaller number of power switches, resulting in a decrease in the multifaceted nature, adding to the cost and weight of the inverter. Finally, near sinusoidal voltages and roughly simple frequency switching can be produced.

Focus on modelling and simulating the single-phase inverter as a Pulse Width Modulation (PWM) modulated frequency changer in. A circuit that transforms DC sources into AC sources is an inverter. Pulse width modulates a system that uses the inverter circuit as a means to minimise overall harmonic distortion. The effects of Harmonics in the Power System and measures to minimise the effects of Harmonics are clarified by a newly updated seven-level cascaded h-bridge inverter, as well as how Harmonic distortion is one of the most severe power quality concerns and causes many power system disruptions

A new hybrid inverter is suggested that uses six active switches to synthesise 7-level waveform in asymmetric source configuration. It will require a cascaded H-bridge inverter with a similar source design. Eight working switches, both running at high frequency switching frequencies.

A new hybrid 7-level topology is proposed in this article, which consists of two flipped sources linked to sequence. The paper explains the functioning of the proposed structure. In order to maximise the switching frequencies of different switches with different voltage pressures, a multicarrier PWM system has been implemented. While the highest stress

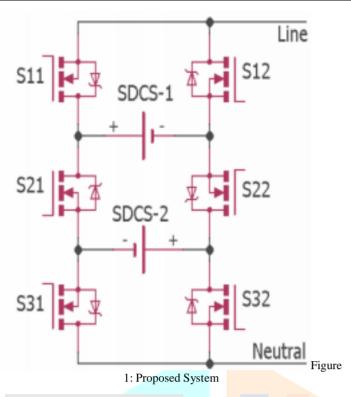

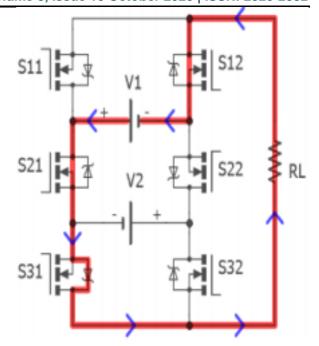

dependent second source and some controllers have been designed to keep the voltage (V2) constant at the one-third level of the reference voltage (V1). As it is shown in figure 1, six switches are used to produce voltage states listed in table I.

switches operate at the fundamental level, the lowest stress switches operate at the frequency of the carrier.

A reduction of the number of switches and conduction losses is presented in [25]. The operation and performance of the proposed multilevel inverter has been ascertained through simulations and verified experimentally for single phase nine-level multilevel inverter. Moreover, a 15-level inverter with asymmetric source configuration has been also investigated for charge balance control using the proposed modulation scheme in this paper with a view to reduce the device count and to obtain all possible additive and subtractive combinations of the input DC levels in the output voltage waveform.

Two new topologies of a 7-level cascaded multilevel inverter with a lower number of switches are proposed by A than the conventional type with 12 switches[27]. The topology consists of 9-switch circuits and 7 switches for the same 7-level output. In this article, a new topology is observed in either case, with 7 switches added and the same 7-level performance.

At production, a single unit can produce two positive and a zero degree. Since this simple unit will establish positive levels, H-bridge is also linked to it for negative levels. This is an integrated multi-level H-bridge cascading inverter. The developed single stage cascaded multilevel inverter enables multilevel generation with a reduced number of component power switching components There is also a reduction in the number of driver circuits required, low dv / dt stress on individual switches, and also a reduction in switching losses. It needs less DC voltage sources than traditional cascaded multilevel inverters

### III. PROPOSED SYSTEM

Simulation research has shown that during the process, this switch design induces current flow to the second DC bus, making it unavoidable to use a series diode as a reverse voltage blocking system. Using a storage energy unit as the second DC bus and regulating its voltage so that the desired voltage levels are produced at the output is the best way to solve this problem. Hence, Voltage Source V2 has been placed in the topology as the

S1 S2 S3 S1' S2' S3' OUTPUT **\*\*\* \*\*\*\* \*\*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\* \*\*\***

110 V2 2Vdc 101010 V1+V2 3Vdc 11100000 000111

0 0 0 1 1 1 0 0 -V<sub>2</sub> -Vdc 1 1 0 0 0 1 -V<sub>2</sub> -2Vdc

#### 0 1 0 1 0 1 -V2-V1-3Vdc

Table I.1Switching States and Voltage Levels of the CSC Inverter

It is clear from the table I that the switches S1', S2' and S3' works reversely respect to the switches S1, S2 and S3 due to preventing the short circuit on DC buses. Although different voltage levels can be generated by the CHB ML

Inverter using different DC voltage sources, to achieve the maximum voltage levels at the output (Vab), the second DC bus

amplitude must be one third of the first DC bus (V1=3V2). Thus, Vab would have seven voltage levels including  $0, \pm V2, \pm 2V2, \pm 3V2$ .

The fundamental theory of switching topology is to use the power electronics switches to isolate the DC sources from the load. With the assistance of MOSFET, two asymmetric DC sources are connected in series in such a way that the lower potential source terminal V1 is connected with the higher potential source terminal V2 of the other source DC. And two independent asymmetric DC voltages are chosen in such a way that V2 = 2V1.

#### MODES OF OPERATION

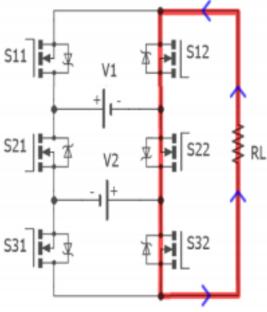

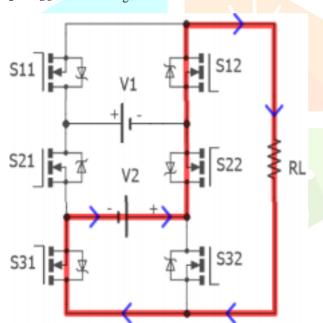

**Mode1:** The switches S12, S22, S32 are turned on, there is no input supply hence the output is 0 i'e  $V_0(t) = 0$ , as shown in figure 2.

Figure 2: Mode

1 Zero output Voltage

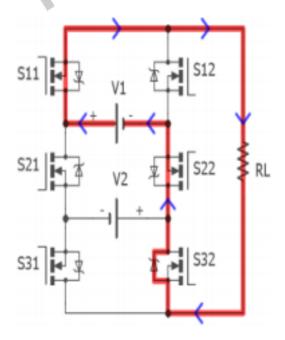

Mode2: The switches S11, S22,S32 are turned on and the supply will be given through  $V_1$  source and the output voltage is  $V_0(t) =$  $V_1 = V_{DC}$ , as shown in the figure 3

3

Figure 3: Mode2 Vdc

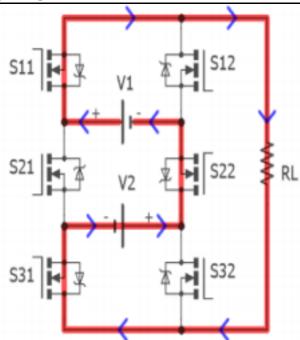

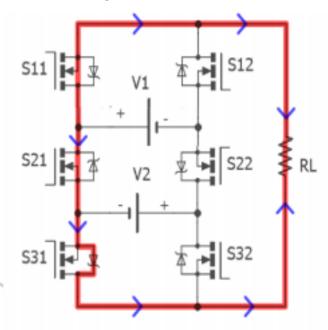

**Mode3:** The input voltage is  $V_2$  and the switches S12, S22 and S31 starts conducting and the output will be i'e V0(t) =  $V_2$ = 2 $V_D$ cas shown in figure 4.

Figure 4: Mode 3 for 2Vdc

**Mode 4:**For  $3V_{DC}$ , input supply is given through both the voltage source and S11, S22, S31 are conducting and obtained output will be  $V_0(t) = V_1 + V_2 = 3V_{DC}$  as shown in figure 5.

Figure 5: Mode 4 for 3Vdc

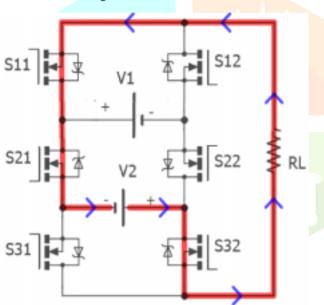

Figure 6: Mode 5 for output zero

**Mode 5:**In this mode the switches S11, S21, S31 are on but there is no input supply hence output will be 0 that is  $V_0(t)=0$  as shown in figure 6

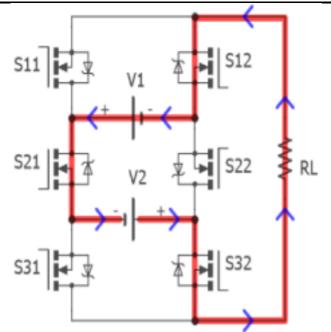

**Mode 6:**In the input voltage is  $V_1$  and the switches S12, S21 and S31, start conducting and the output will be V0(t) = -V1=-VDC, as shown in figure 7.

Figure 7: Mode 6 for -Vdc

Mode 7: The input voltage is V<sub>2</sub> and the switches S11, S21 and S32, start conducting and the output will be  $V0(t) = -V_2$ =-2V<sub>DC</sub>as shown in figure 8.

Figure 8: Mode 7 for -2Vdc

Mode 8:For -3V<sub>DC</sub>, input supply is given through both the voltage sources and S12, S21, S32are conducting and obtained output will be  $V_0(t) = -V_1-V_2=-3V_{DC}$ as shown in figure 9

Figure 9: Mode 8 for -3Vdc

#### IV. SIMULATION RESULTS

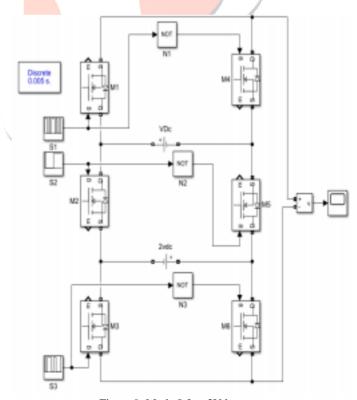

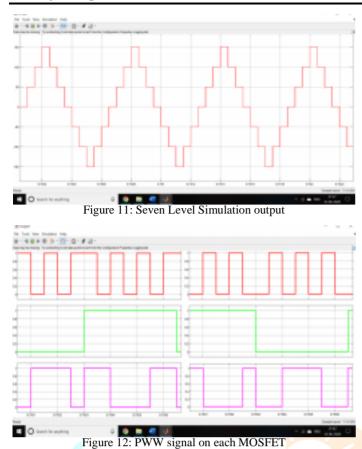

The proposed multilevel inverter is built on the MATLAB / Simulink platform, a simulation model of a single-phase modified seven-level cascaded H-bridge inverter. The simulation is being done for the proposed topology by using seven MOSFET switches respectively as shown in figure 10 and its simulation output is shown in the figure 11 While the carrier frequency of the sinusoidal reference is taken as 50hz.

Figure 9: Mode 8 for -3Vdc

#### V. CONCLUSIONS

A newly updated seven-level cascaded H-bridge inverter with reduced components has been developed, enabling multilevel generation with a reduced number of power switching components. So on the person turn, there is also reduction number driver circuit needed low dv / dt tension, switching losses also decreased. Fewer DC voltage sources were necessary than traditional cascaded multilevel inverters.

A new modified seven level cascaded H-bridge inverter with reduced components It is simulated and it is concluded that the suggested ML inverter needs only 6 switches to achieve the same 7-level output voltage, whereas the traditional type requires 8 switches. If the output voltage level is further increased, this difference will be greater. The proposed seven-level modified cascaded H-bridge inverter will therefore remove approximately half the number of switches, relative to the present cascaded multilevel inverter counterparts, their gate drivers.

The model is applied using tools from MATLAB / SIMULINK. The operating system of the inverter is extensive and is illustrated with simulink. The proposed model therefore promises better or more reliable efficiency

IEEE Journal Emerg. and Select. Topics in Power Electron., vol. 4, no. 2, pp. 435-444, 2016.

[15]. H. Vahedi, A. Shojaei, L.-A. Dessaint, and K. Al Haddad,

with less switching loss and overall harmonic distortion. The simulation is done using the programme MATLAB / SIMULINK. By simulation outcomes, the idea that is predicted is confirmed. The overall cost and complexity of the circuit has declined.

#### VI. REFERENCES

[1]. B. Singh, A. Chandra, and K. Al-Haddad, Power Quality: Problems and Mitigation Techniques: John Wiley & Sons, 2014. [2]. I. Gowaid, G. Adam, A. Massoud, S. Ahmed, and B. Williams,

"Hybrid and Modular Multilevel Converter Designs for Isolated HVDC-DC Converters," IEEE Journal Emerg. and Select. Topics in Power Electron., vol. PP, no. 99, p. 1, 2017.

[3]. H. Vahedi, K. Al-Haddad, Y. Ounejjar, and K. Addoweesh, "Crossover Switches Cell (CSC): A New Multilevel Inverter Topology with Maximum Voltage Levels and Minimum DC Sources," in IECON 2013-39th Annual Conference on IEEE Industrial Electronics Society, Austria, 2013, pp. 54-59.

[4]. P. W. Hammond, "A new approach to enhance power quality for medium voltage drives," in Petroleum and Chemical Industry Conference, 1995. Record of Conference Papers., Industry Applications Society 42nd Annual, 1995, pp. 231-235.

[5]. A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-pointclamped PWM inverter," IEEE Trans. Ind. Applications, no. 5, pp. 518-523, 1981.

[6]. M. Sharifzadeh, H. Vahedi, A. Sheikholeslami, P.- A. Labbé, and K. Al-Haddad, "Hybrid SHM-SHE Modulation Technique for Four-Leg NPC Inverter with DC Capacitors Self-Voltage-Balancing," IEEE Trans. Ind. Electron., vol. 62, no. 8, pp. 4890-4899, 2015.

[7]. F. Sebaali, H. Vahedi, H. Y. Kanaan, N. Moubayed, and K. Al-Haddad, "Sliding Mode Fixed Frequency Current Controller Designed for GridConnected NPC Inverter," IEEE Journal Emerg. and Select. Topics in Power Electron., vol. 4, no. 4, pp. 1397-1405,

[8]. M. Sharifzadeh, H. Vahedi, R. Portillo, M. Khenar, Sheikholeslami, L. G. Franquelo, et al., "Hybrid SHM-SHE Pulse Amplitude Modulation for High Power Four-Leg Inverter," IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7234-7242, 2016.

[9]. H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Mediumvoltage multilevel converters—State of the art, challenges, and requirements in industrial applications," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2581-2596, 2010.

[10]. B. Fernandes, "A Fault-Tolerant Single-Phase Grid Connected Inverter Topology with Enhanced Reliability for Solar PV Applications," IEEE Journal Emerg. and Select. Topics in Power Electron., vol. 5, no. 3, pp. 1254-1262, 2017.

[11]. R. Kumar and B. Singh, "Single Stage Solar PV Fed Brushless DC Motor Driven Water Pump," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 3, pp. 1377-1385, 2017.

[12]. Enerdata. Global Energy Statistical Yearbook 2015 [Online]. Available: <a href="http://yearbook.enerdata.net/">http://yearbook.enerdata.net/</a> [13]. J. A. Y. Poissant; and J. Hiscock;, "National Survey Report of PV Power Application in Canada," INTERNATIONAL ENERGY AGENCY2012. [14]. N. Kumar, T. K. Saha, and J. Dey, "Sliding-mode control of PWM dual inverter-based grid-connected PV system: modeling and performance analysis,"

"Reduced DC Link Voltage Active Power Filter Using Modified PUC5 Converter," IEEE Trans. Power Electron., vol. 33, no. 2, pp. 943-947, 2018.

[16]. S. Daher, J. Schmid, and F. L. Antunes, "Multilevel inverter topologies for stand-alone PV systems," IEEE Trans. Ind. Electron., vol. 55, no. 7, pp. 2703-2712, 2008

[17]. H. Nademi, A. Das, R. Burgos, and L. E. Norum, "A new circuit performance of modular multilevel inverter suitable for photovoltaic conversion plants," IEEE Journal Emerg. and Select. Topics in Power Electron., vol. 4, no. 2, pp. 393-404, 2016.

[18]. J. T. Hawke, H. S. Krishnamoorthy, and P. N. Enjeti, "A family of new multiport power-sharing converter topologies for large grid-connected fuel cells," IEEE Journal Emerg. and Select. Topics in Power Electron., vol. 2, no. 4, pp. 962-971, 2014.

[19]. K. Al-Haddad, Y. Ounejjar, and L. A. Gregoire, "Multilevel Electric Power Converter," US Patent 20110280052, 2011.

[20]. M. Trabelsi, S. Bayhan, K. A. Ghazi, H. Abu-Rub, and L. Ben-Brahim, "Finite-control-set model predictive control for grid-connected packed-U-cells multilevel inverter," IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7286-7295, 2016.

[21]. Anil Kumar Yarlagadda1, Vargilkumar Eate2, Y.S.Kishore Babu3, Abanishwar Chakraborti4, "A Modified Seven Level Cascaded H Bridge Inverter" 2018 5th IEEE Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering 978-1-5386-5002-8/18/\$31.00 ©2018 IEEE

[22]. P.ASalodkar, P.S.Kulkani "A single phase seven level inverter topology for photovoltaic application". IEEE international

conference on power & embedded drive control (ICPEDC) 26 October 2017

[23]. Radhakrishnas, Jayakumarsahoo, saradhaaprasannas ahoo, "Harmonic analysis of single phase inverter" IJAREEIE, vol. 5, issue 2, February 2016.

[24]. Krishna kumarGupta, Lalitkumar, Shailenra Jain; "A new seven level hybrid inverter" IEEE Conference on power electronics, and Energy systems. december 16,2012.

[25]. Gupta, K.K.; Jain, S.; , "Topology for multilevel inverters to attain maximum number of levels from given DC sources" ,Power Electronics, IET, vol.5, no.4, pp.435-446, April 2012

[26]. J. Napoles, A. J. Watson, and J. J. Padilla, "Selective harmonic mitigation technique for cascaded H bridge converter with nonequal dc link voltages," IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1963–1971, May 2013.

[27]. T V V S Lakshmi ,Noby George, Umashankar S and Kothari D P "Cascaded seven level inverter with reduced number of switches using level shifting PWM technique" 2013 international conference on power, energy and control (ICPEC) 978-1-4673- 6030-2/13/\$31.00 ©2013 IEEE

[28]. Sarala S. Wale, Sunil K.Patil, "A Developed Single Phase Cascaded Multilevel Inverter with Reduced Number of Power Switches" 978-1-5090-3239- 6/17/\$31.00©2017IEEE